# Preliminary Draft of Accelerated Graphics Port Interface Specification

Preliminary Draft of Revision 2.0 Intel Corporation December 10, 1997

Intel may have patents and/or patent applications related to the various Accelerated Graphics Port (AGP or A.G.P.). interfaces described in the *Accelerated Graphics Port Interface Specification*. A reciprocal, royalty-free license to the electrical interfaces and bus protocols described in, and required by, the *Accelerated Graphics Port Interface Specification Revision 2.0* will be available from Intel.

12/10/97-- 3:58 PM

Accelerated Graphics Port Interface Specification Copyright © Intel Corporation 1996-1997 All rights reserved.

THIS SPECIFICATION IS PROVIDED"AS IS" WITH NO WARRANTIES WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED OR INTENDED HEREBY

INTEL DISCLAIMS ALL LIABILITY INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTSRELATING TO USE OF INFORMATION IN THIS SPECIFICATION INTEL DOES NOT WARRANT OR REPRESENT THAT SUCH USE WILL NOT INFRINGE SUCH RIGHTS.

\*THIRD-PARTY BRANDS AND NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS

## Contents

| 1. Introduction                                  |    |

|--------------------------------------------------|----|

| 1.1 Motivation                                   |    |

| 1.2 Relationship to PCI                          |    |

| 1.3 Terminology                                  |    |

| 2. Architectural Context and Scope               | 21 |

| 2.1 Two Usage Models: "Execute" and "DMA"        |    |

| 2.2 Queuing Models                               |    |

| 2.3 Performance Considerations                   | 24 |

| 2.4 Platform Dependencies                        |    |

| 3. Signals and Protocol Specification            | 29 |

| 3.1 Pin Description                              |    |

| 3.1.1 Semantics of PCI Signals                   |    |

| 3.1.2 Configuration of an A.G.P. Master          |    |

| 3.1.2.1 Device for A.G.P. Only Operation         |    |

| 3.1.2.2 Device for Both PCI and A.G.P. Operation |    |

| 3.2 Operation Overview                           |    |

| 3.2.1 Pipeline Operation                         |    |

| 3.2.2 Addressing Modes and Bus Operations        | 41 |

| 3.3 Bus Commands                                 |    |

| 3.4 Access Ordering Rules                        | 44 |

| 3.4.1 Ordering Rules and Implications            | 44 |

| 3.4.2 Deadlock Avoidance                         |    |

| 3.4.3 Flush and Fence Commands                   |    |

| 3.4.4 Access Request Priority                    |    |

| 3.5 Bus Transactions                             | 51 |

| 3.5.1 Enqueueing Requests                        | 51 |

| 3.5.1.1 Address Demultiplexing Option            | 51 |

| 3.5.1.2 AD Bus                                   | 55 |

| 3.5.1.3 64-bit Requests on the AD Bus            |    |

| 3.5.2 Flow Control                               |    |

| 3.5.2.1 Address Flow Control                          |     |

|-------------------------------------------------------|-----|

| 3.5.2.2 Data Flow Control                             |     |

| 3.5.2.2.1 Read Flow Control                           |     |

| 3.5.2.2.2 Write Data Flow Control                     | 67  |

| 3.5.2.3 Other Flow Control Rules                      |     |

| 3.5.3 Data Transactions                               |     |

| 3.5.3.1 1x Data Transfers                             |     |

| 3.5.3.2 2x Data Transfers                             |     |

| 3.5.3.3 Relationship Between xRDY# and AD_STBx        |     |

| 3.5.3.4 4x Data Transfers                             |     |

| 3.5.3.5 Fast Write Transfers                          |     |

| 3.5.3.5.1 FW Basic Transaction                        |     |

| 3.5.3.5.1.1 FW Transactions with Waitstates           |     |

| 3.5.3.5.2 FW Transaction with Different Terminations  |     |

| 3.5.3.5.2.1 Retry                                     |     |

| 3.5.3.5.2.2 Disconnect With Data                      |     |

| 3.5.3.5.2.3 Disconnect Without Data                   |     |

| 3.5.3.5.2.4 Target-Abort                              |     |

| 3.5.3.5.2.5 Master-Abort                              | 91  |

| 3.5.3.5.2.6 Normal                                    |     |

| 3.5.3.5.3 Back to Back Transactions                   |     |

| 3.5.3.5.3.1 FW to FW                                  | 94  |

| 3.5.3.5.3.1.1 Write Buffer Full                       |     |

| 3.5.3.5.3.1.2 DEVSEL# Operation and FW Transactions   |     |

| 3.5.3.5.3.2 FW to PCI <sub>c</sub> Read               |     |

| 3.5.3.5.3.3 PCI <sub>c</sub> Read to FW               |     |

| 3.5.3.5.3.4 FW to A.G.P. Read                         |     |

| 3.5.3.5.3.5 A.G.P. Read to FW                         | 106 |

| 3.5.3.5.3.6 FW to A.G.P. Write                        | 107 |

| 3.5.3.5.3.7 A.G.P. Write Followed by FW               |     |

| 3.5.3.5.3.8 FW Followed by Graphics PCI Master Read   | 110 |

| 3.5.3.5.3.9 Graphics PCI Master Read Followed by FW   |     |

| 3.5.3.5.3.10 FW Followed by Graphics PCI Master Write | 112 |

| 3.5.3.5.3.11 Graphics PCI Master Write Followed by FW           |  |

|-----------------------------------------------------------------|--|

| 3.5.3.5.3.12 FW Followed by PIPE#                               |  |

| 3.5.3.5.3.13 PIPE# Followed by FW                               |  |

| 3.5.3.5.3.13.1 PIPE# Followed by FW with Delay                  |  |

| 3.6 Arbitration                                                 |  |

| 3.6.1 Introduction                                              |  |

| 3.6.2 Master's REQ#                                             |  |

| 3.6.3 GNT# and ST[2::0]                                         |  |

| 3.6.4 A.G.P. Master                                             |  |

| 3.6.4.1 A.G.P. Master Initiating an A.G.P. Request.             |  |

| 3.6.4.2 A.G.P. Master Initiating a PCI Transaction              |  |

| 3.6.5 A.G.P. Arbiter                                            |  |

| 3.6.6 GNT# Pipelining                                           |  |

| 3.6.6.1 Pipelining GNT#s                                        |  |

| 3.6.6.2 A Request Transaction Followed by a Request Transaction |  |

| 3.6.6.3 A Request Transaction Followed by a Data Transfer.      |  |

| 3.6.6.4 A Data Transfer Followed by a Request                   |  |

| 3.6.6.5 A Data Transfer Followed by a Data Transfer             |  |

| 3.7 Error Reporting                                             |  |

| 3.8 Special Design Considerations                               |  |

| 4. Electrical Specification                                     |  |

| 4.1 Overview                                                    |  |

| 4.1.1 Introduction                                              |  |

| 4.1.2 Transfer Mode Operation                                   |  |

| 4.1.2.1 Transfer Mode Signaling Levels                          |  |

| 4.1.2.2 1X Transfer Mode Operation                              |  |

| 4.1.2.3 2X Transfer Mode Operation                              |  |

| 4.1.2.4 4X Transfer Mode Operation                              |  |

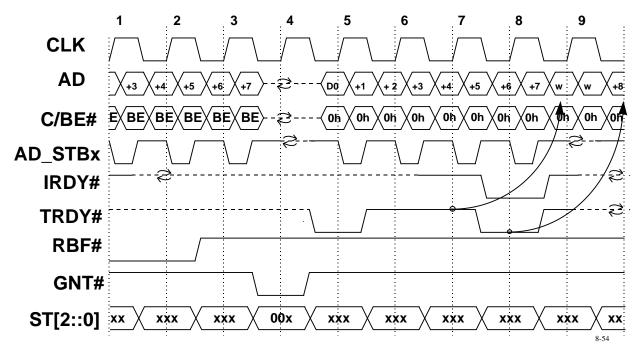

| 4.1.2.5 2X/4X Timing Model                                      |  |

| 4.1.2.6 Transmit/Receive Outer Loop                             |  |

| 4.1.2.7 Transmit to Receive Inner loop                          |  |

| 4.1.2.8 Transmit Outer to Inner Loop                            |  |

| 4.1.2.9 Receive Inner to Outer Loop                             |  |

| 4.1.2.10 SB_STB Synchronization                  |     |

|--------------------------------------------------|-----|

| 4.2 Component Specification                      |     |

| 4.2.1 DC Specifications                          |     |

| 4.2.1.1 A.G.P. 1X Mode DC Specification          |     |

| 4.2.1.2 2X and 4X Mode DC Specification          |     |

| 4.2.2 AC Timings                                 |     |

| 4.2.2.1 A.G.P. 1X Timing Parameters              |     |

| 4.2.2.2 A.G.P. 2X AC Timing Parameters           |     |

| 4.2.2.3 4X AC Timing Parameters                  |     |

| 4.2.3 Measurement and Test Conditions            |     |

| 4.2.3.1 1X Mode Measurements                     |     |

| 4.2.3.2 2X Mode Measurements                     |     |

| 4.2.3.3 4X Mode Measurements                     |     |

| 4.3 General System Specifications                |     |

| 4.3.1 Physical Requirements                      |     |

| 4.3.2 Clock Skew                                 |     |

| 4.3.3 Reset                                      |     |

| 4.3.4 Interface Signaling                        |     |

| 4.3.5 Motherboard / Add-in Card Interoperability |     |

| 4.3.6 Pull-ups                                   |     |

| 4.3.7 Maximum AC Ratings and Device Protection   |     |

| 4.3.8 Power Supply Delivery                      | 179 |

| 4.3.9 USB Design Considerations                  |     |

| 4.4 1X and 2X Transfer Mode Specifications       |     |

| 4.4.1 Signal Integrity Requirement               |     |

| 4.4.2 1X and 2X Mode Driver Characteristics      |     |

| 4.4.3 1X and 2X Mode Receiver Characteristics    |     |

| 4.4.4 Component Pinout Recommendations           |     |

| 4.4.5 1X and 2X Mode Motherboard Specifications  |     |

| 4.4.5.1 System Timing Budget                     |     |

| 4.4.5.2 Interconnect Delay                       |     |

| 4.4.5.3 Physical Requirements                    |     |

| 4.4.5.4 Signal Routing and Layout                |     |

| 4.4.5.5 Crosstalk Consideration                      |  |

|------------------------------------------------------|--|

| 4.4.5.6 Impedances                                   |  |

| 4.4.5.7 Vref Generation                              |  |

| 4.4.5.8 Line Termination                             |  |

| 4.4.6 1X and 2X Mode Add-in Card Specifications      |  |

| 4.4.6.1 Clock Skew                                   |  |

| 4.4.6.2 Interconnect Delay                           |  |

| 4.4.6.3 Physical Requirements                        |  |

| 4.4.6.4 Pin Assignment                               |  |

| 4.4.6.5 Signal Routing and Layout                    |  |

| 4.4.6.6 Impedances                                   |  |

| 4.4.6.7 Vref Generation                              |  |

| 4.5 4X Mode Specifications                           |  |

| 5. Mechanical Specification                          |  |

| 5.1 Introduction                                     |  |

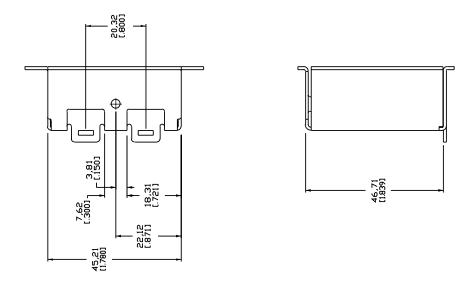

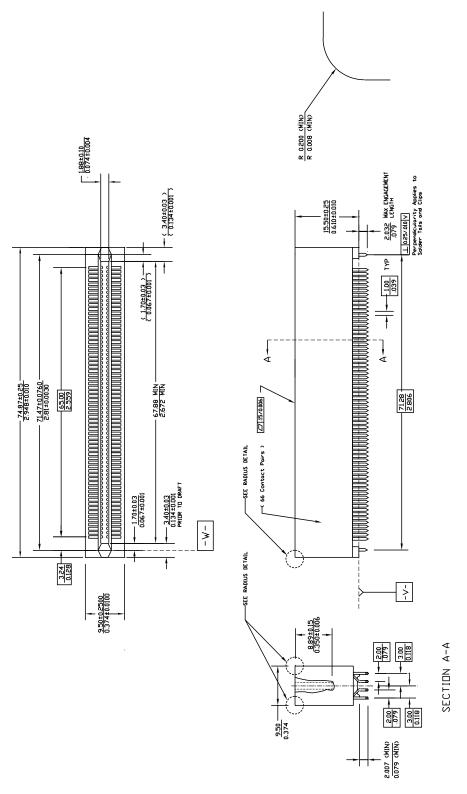

| 5.2 Expansion Card Description                       |  |

| 5.2.1 Physical Dimensions and Tolerances             |  |

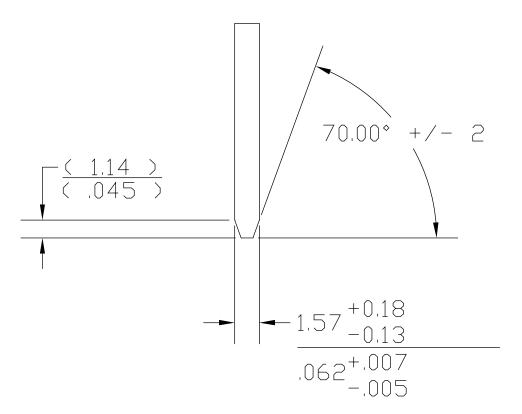

| 5.2.2 Contact Design                                 |  |

| 5.3 Thermal Specification                            |  |

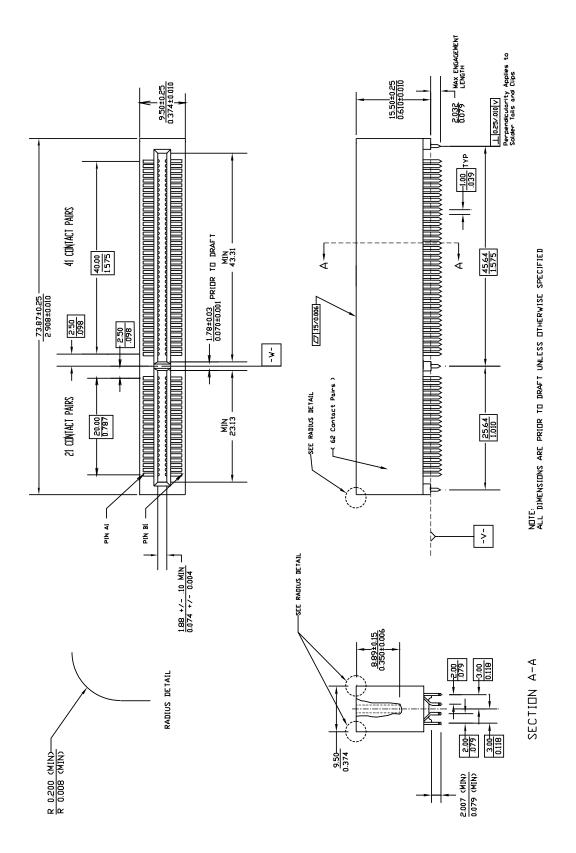

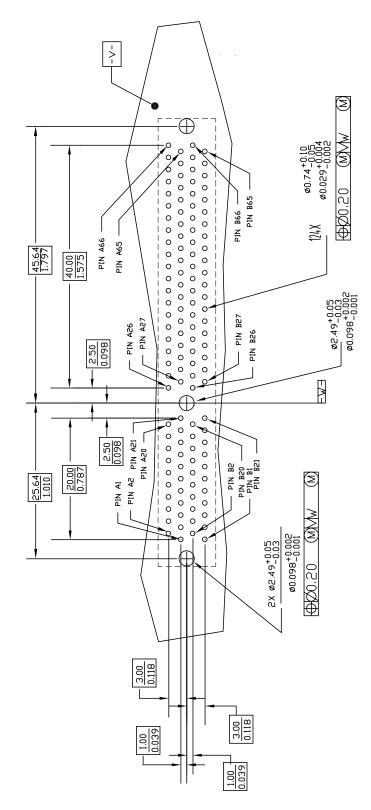

| 5.4 A.G.P Add-in Card Connector Physical Description |  |

| 5.4.1 Add-in Card Edge Dimensions                    |  |

| 5.4.2 Insertion/Extraction Force                     |  |

| 5.4.3 Assembly Requirements to Motherboard           |  |

| 5.4.3.1 Pre-Solder Attachment                        |  |

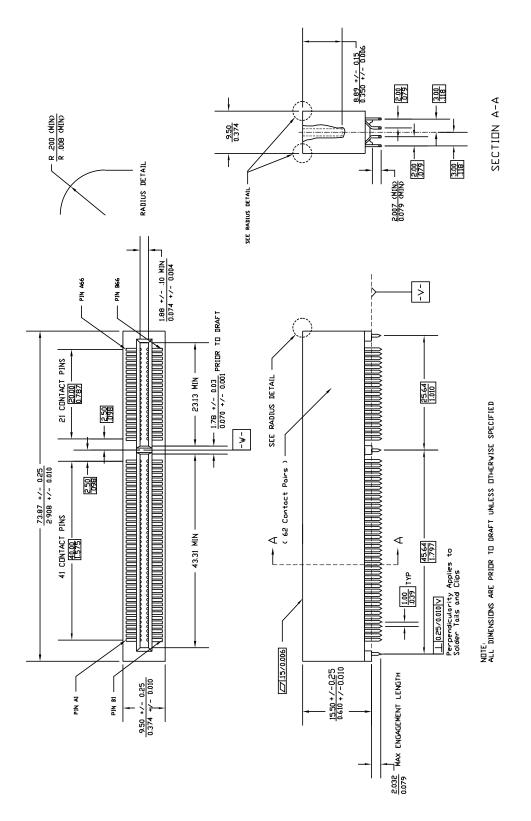

| 5.4.3.2 Solder Tail Design and Alignment:            |  |

| 5.4.3.3 Contact Backout Wipe                         |  |

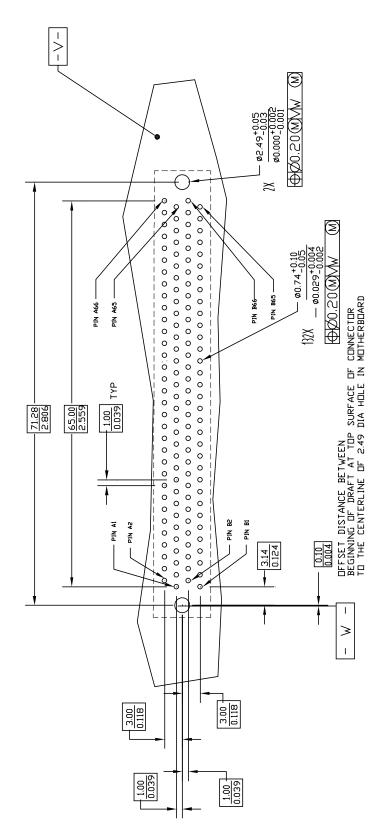

| 5.4.4 A.G.P Add-in Card 3.3 Volt Connector           |  |

| 5.4.5 A.G.P Add-in Card Universal Connector          |  |

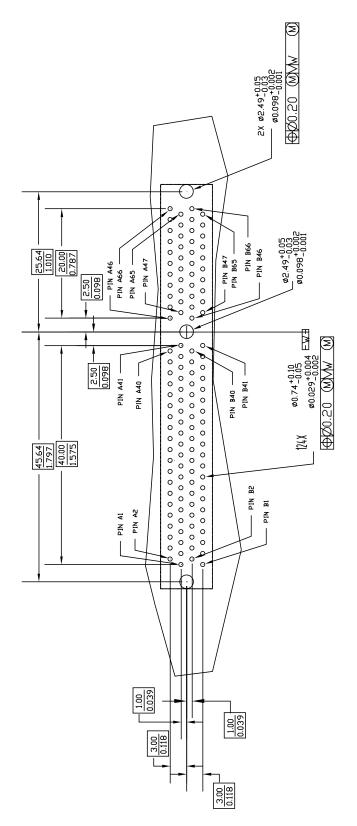

| 5.4.6 A.G.P Add-in Card 1.5 Volt Connector           |  |

| 5.4.7 A.G.P Add-in Card Planar Implementation        |  |

| 5.4.7.1 ATX Planar Implementation                    |  |

| 5.4.7.2 NLX Planar Implementation                    |  |

| 5.5 Connector Pinout                                 |  |

| 5.6 A.G.P Connector Electrical Requirements                                |  |

|----------------------------------------------------------------------------|--|

| 5.6.1 Determination of Averaged Contact Resistance                         |  |

| 5.6.1.1 Bulk Resistance                                                    |  |

| 5.6.1.2 Initial Contact Resistance                                         |  |

| 5.6.1.3 Final Contact Resistance                                           |  |

| 5.6.1.4 Test Voltage and Current Rating                                    |  |

| 5.6.2 Contact Current Rating                                               |  |

| 5.6.3 Effective Inductance                                                 |  |

| 5.6.4 Pin-to Pin-Capacitance                                               |  |

| 5.6.5 Pin-to-Pin Insulation Resistance                                     |  |

| 5.6.6 Dielectric Withstand Voltage                                         |  |

| 5.6.7 Characteristic Impedance, Propagation, and Crosstalk Coupling        |  |

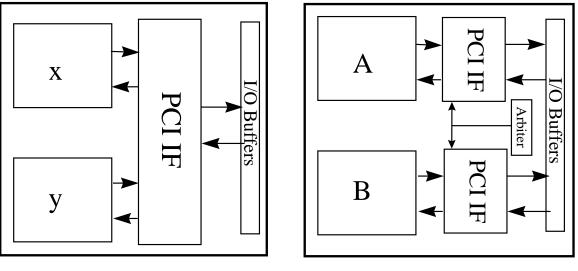

| 5.6.7.1 Connector Impedance, Propagation Delay, and Crosstalk Measurements |  |

| 5.6.7.2 Impedance and Propagation Delay                                    |  |

| 5.6.7.3 Crosstalk                                                          |  |

| 5.7 A.G.P Connector Environmental Requirements                             |  |

| 5.7.1 Temperature Range                                                    |  |

| 5.7.1.1 Operating                                                          |  |

| 5.7.1.2 Shipping and Storage                                               |  |

| 5.7.1.3 Temperature Life                                                   |  |

| 5.7.2 Visual Inspection                                                    |  |

| 5.7.3 Vibration, Random                                                    |  |

| 5.7.4 Shock                                                                |  |

| 5.7.5 Durability                                                           |  |

| 5.7.6 Mating Force                                                         |  |

| 5.7.7 Unmating Force                                                       |  |

| 5.7.8 Thermal Shock                                                        |  |

| 5.7.9 Humidity Temperature Cycling                                         |  |

| 5.7.10 Temperature Life                                                    |  |

| 5.7.11 Mixed Flowing Gas:                                                  |  |

| 5.7.12 Withstand Temperature                                               |  |

| 5.7.13 Porosity                                                            |  |

| 5.7.14 Plating Thickness                                                   |  |

| 5.7.15 Solvent Resistance                               |  |

|---------------------------------------------------------|--|

| 5.7.16 Normal Force                                     |  |

| 5.7.17 Solderability                                    |  |

| 5.7.18 Contact Retention                                |  |

| 5.7.19 Maximum Force on Connector                       |  |

| 5.7.20 Contact Backout Wipe                             |  |

| 5.8 Safety Requirements                                 |  |

| 5.9 Add-in Card Mechanical Sample                       |  |

| 5.10 Connector Qualification                            |  |

| 5.10.1 Sample Size Per Group                            |  |

| 5.10.2 Test Sequence                                    |  |

| 6. System Configuration and A.G.P. Initialization       |  |

| 6.1 POST-time Initialization                            |  |

| 6.1.1 A.G.P. Master Devices                             |  |

| 6.1.2 A.G.P. Target Devices                             |  |

| 6.1.3 Corelogic Ports                                   |  |

| 6.1.3.1 Processor Port                                  |  |

| 6.1.3.2 System Memory Port                              |  |

| 6.1.3.3 PCI Port                                        |  |

| 6.1.3.4 A.G.P. Port                                     |  |

| 6.1.4 Boot-time VGA Display Device(s)                   |  |

| 6.1.5 Operating System Initialization                   |  |

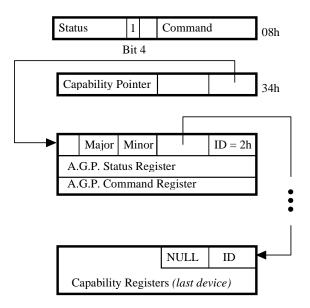

| 6.1.6 PCI Status Register                               |  |

| 6.1.7 Capabilities Pointer - (Offset 34h)               |  |

| 6.1.8 Capability Identifier Register (Offset = CAP_PTR) |  |

| 6.1.9 Status Register (Offset CAP_PTR + 4)              |  |

| 6.1.10 Command Register - (Offset CAP_PTR + 8)          |  |

| 6.2 A.G.P. Master MDA Resource Use Restrictions         |  |

| 6.3 Multifunction A.G.P. Master                         |  |

| 6.3.1 A.G.P. Configuration Registers                    |  |

| 6.3.2 Internal Arbiter                                  |  |

| 6.3.3 Deadlock Avoidance                                |  |

|                                                         |  |

# Figures

| Figure 1-1: System Block Diagram: A.G.P. and PCI Relationship            |    |

|--------------------------------------------------------------------------|----|

| Figure 2-1: Graphics Address Remapping Function                          |    |

| Figure 2-2: A.G.P. Access Queuing Model                                  |    |

| Figure 2-3: Different Corelogic Architectures                            | 25 |

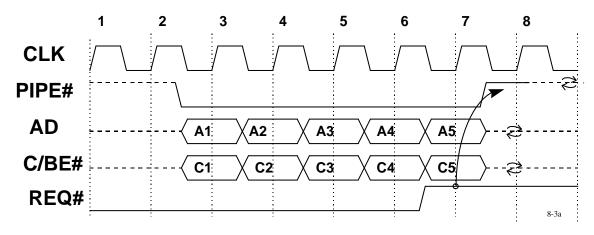

| Figure 3-1: Basic A.G.P. Pipeline Concept                                | 40 |

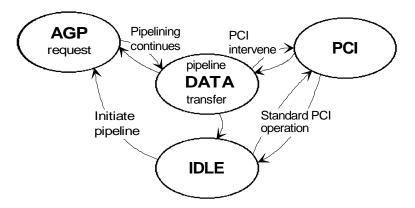

| Figure 3-2: A.G.P./PCI Operational States                                | 40 |

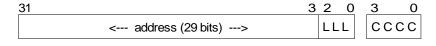

| Figure 3-3: Layout of an A.G.P. Access Request                           |    |

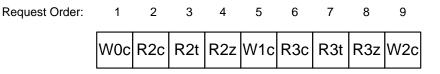

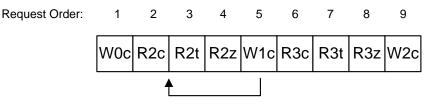

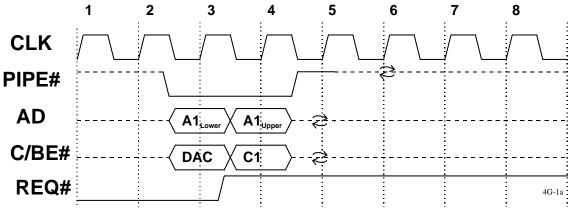

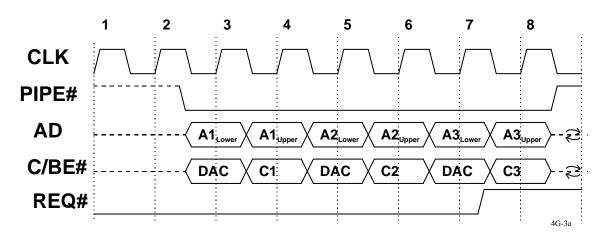

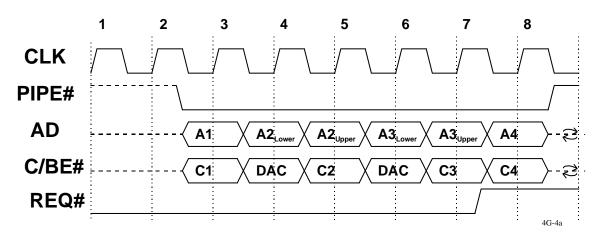

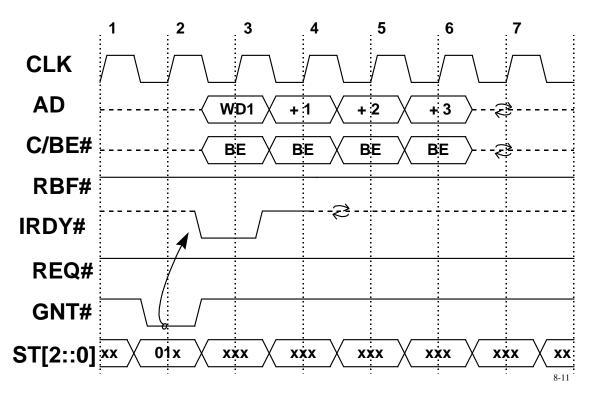

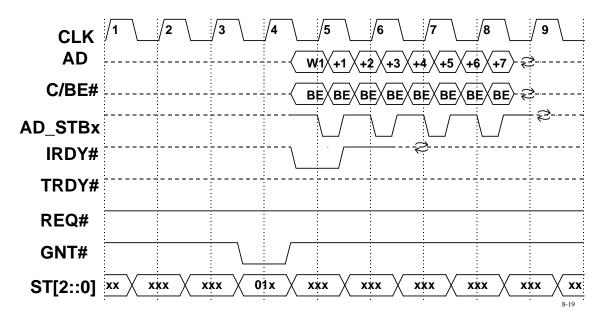

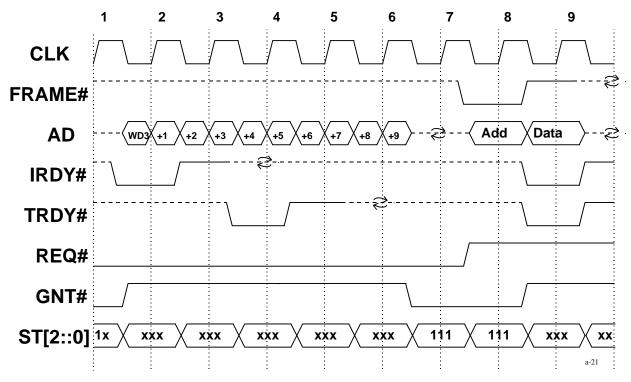

| Figure 3-4: A.G.P. Request                                               | 51 |

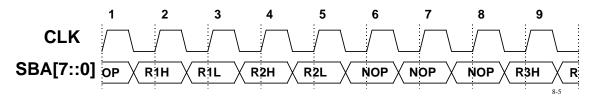

| Figure 3-5: SBA Port Request - 1x                                        |    |

| Figure 3-6: 1x Sideband Addressing                                       |    |

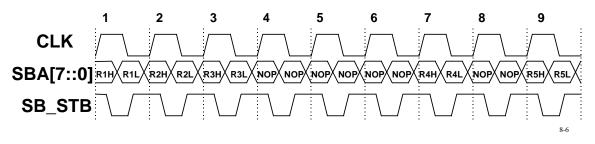

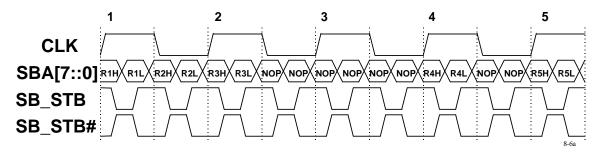

| Figure 3-7: 2x Sideband Addressing                                       | 55 |

| Figure 3-8: 4x Sideband Addressing                                       | 55 |

| Figure 3-9: Single Address                                               |    |

| Figure 3-10: Multiple Addresses Enqueued, Maximum Delay by Master        |    |

| Figure 3-11: Single 64-bit Request                                       | 57 |

| Figure 3-12: Multiple 64-bit Requests                                    |    |

| Figure 3-13: 32-bit and 64-bit Requests                                  |    |

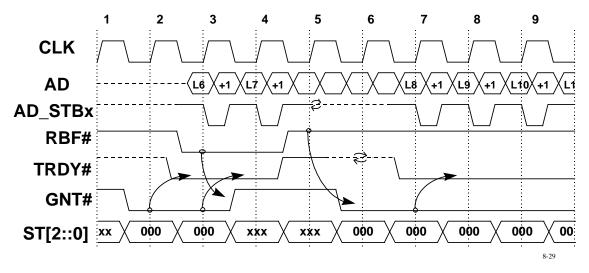

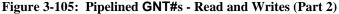

| Figure 3-14: Maximum Number of GNT#s Queued Before the Assertion of RBF# | 65 |

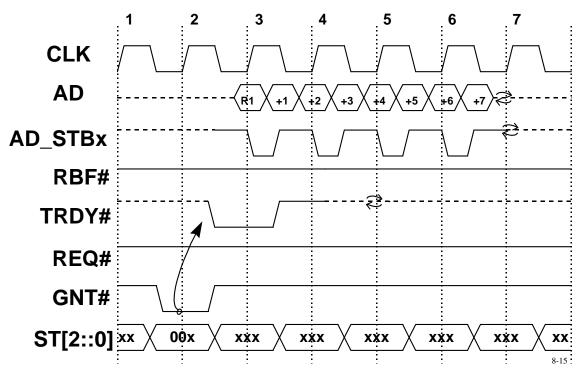

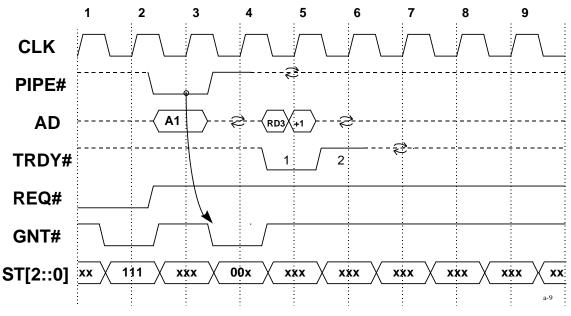

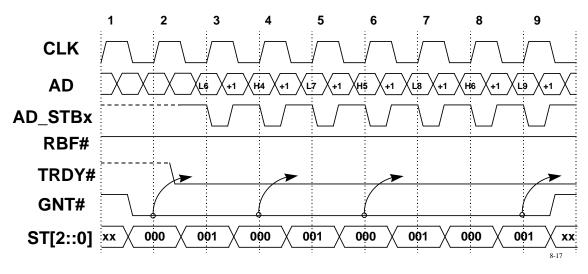

| Figure 3-15: Read Transaction with TP with No Waitstate                  |    |

| Figure 3-16: Read Transaction with TP with a Waitstate                   |    |

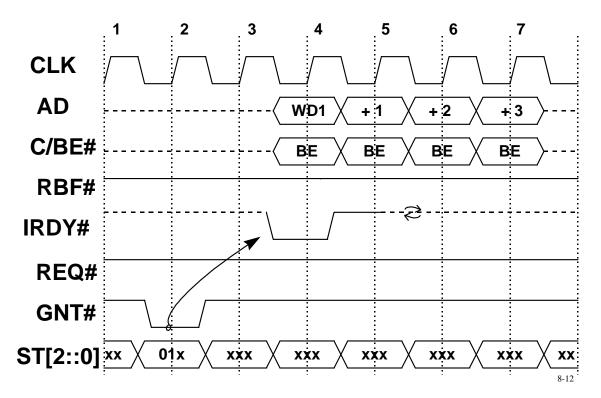

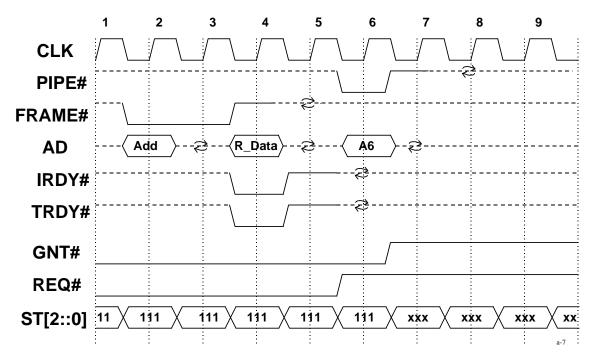

| Figure 3-17: Write Transaction with TP with No Waitstate                 | 67 |

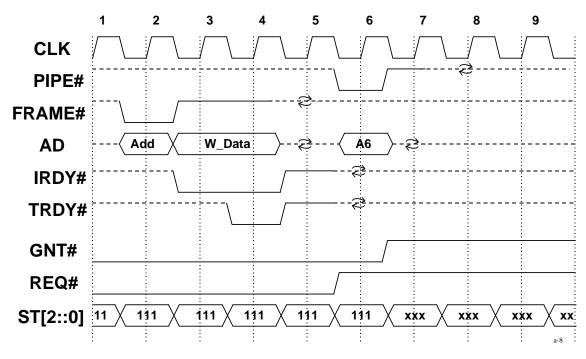

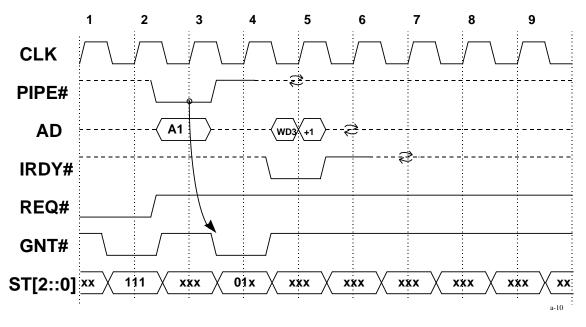

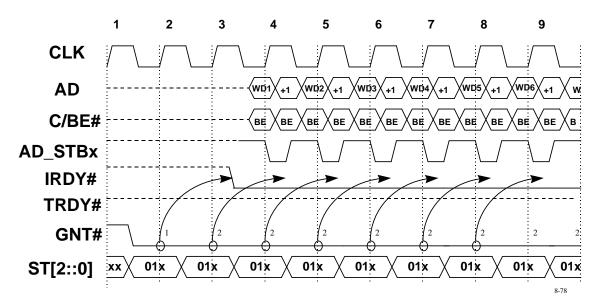

| Figure 3-18: Write Transaction with TP with a Waitstate                  |    |

| Figure 3-19: Maximum Delay by Master on Write Data                       |    |

| Figure 3-20: Write Data with One TP                                      |    |

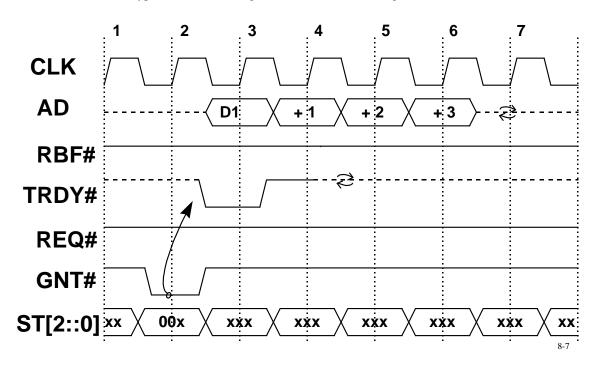

| Figure 3-21: Minimum Delay by Target of Read Transaction                 |    |

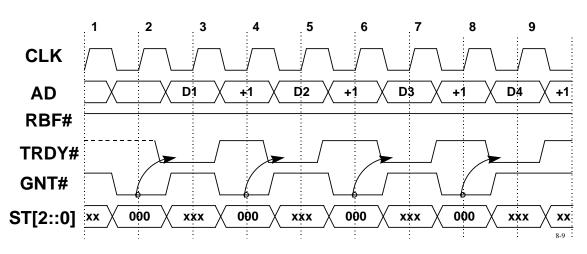

| Figure 3-22: Minimum Delay on Back-to-Back Read Data                     | 71 |

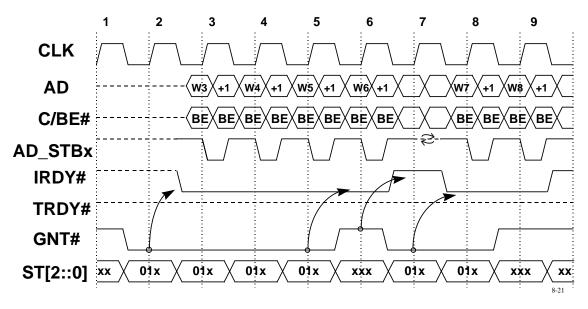

| Figure 3-23: Master Does Not Delay Providing Write Data                  | 72 |

| Figure 3-24: Back-to-Back Write Data Transfers - No Delay                | 73 |

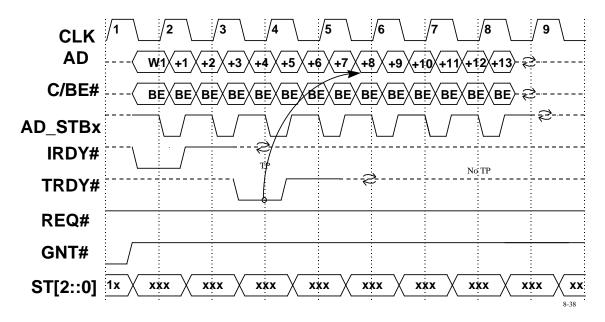

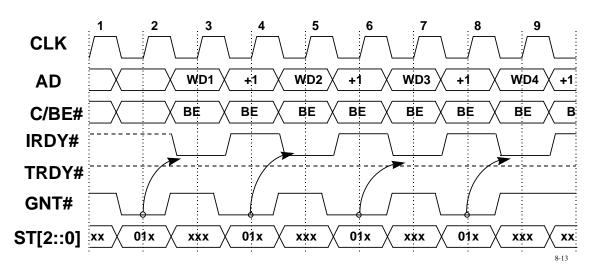

| Figure 3-25: 2x Read Data - No Delay                                     | 74 |

| Figure 3-26: 2x Back-to-Back Read Data - No Delay                        | 74 |

| Figure 3-27:  | 2x Basic Write - No Delay                                   | .75  |

|---------------|-------------------------------------------------------------|------|

| Figure 3-28:  | QuadWord Writes Back-to-Back - No Delay                     | .75  |

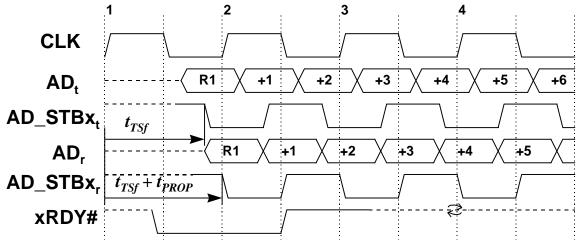

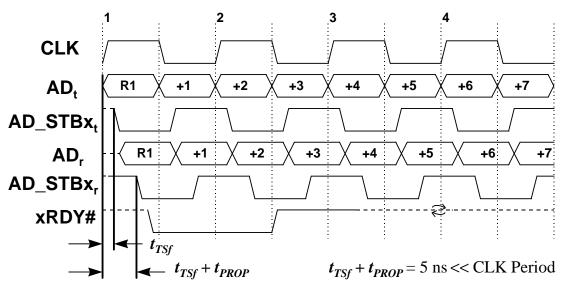

| Figure 3-29:  | Maximum Shift Between xRDY# and AD_STBx                     | .76  |

| Figure 3-30:  | Minimum Shift Between xRDY# and AD_STBx                     | .77  |

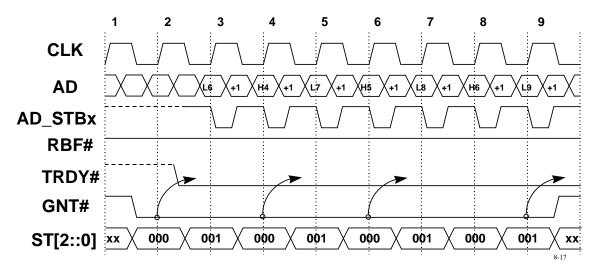

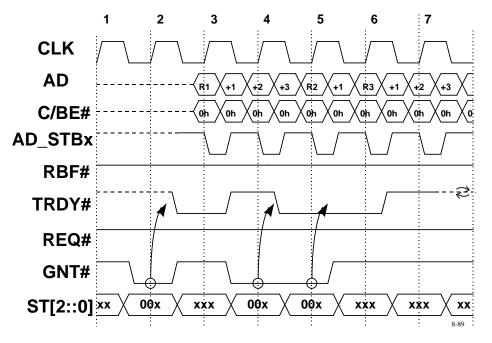

| Figure 3-31:  | 4x Read Data - No Delay                                     | .78  |

| Figure 3-32:  | 4x Back-to-Back Read Data - No Delay                        | . 79 |

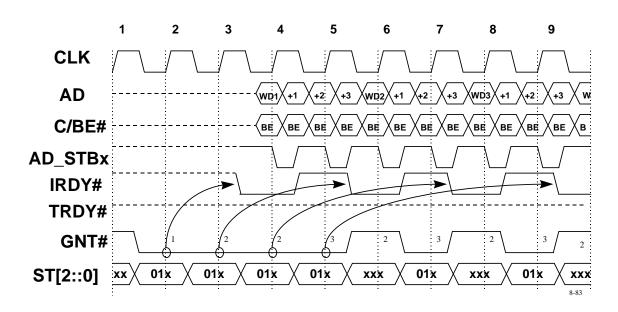

| Figure 3-33:  | 4x Basic Write - No Delay                                   | . 80 |

| Figure 3-34:  | 4x QuadWord Writes - No Delay                               | . 81 |

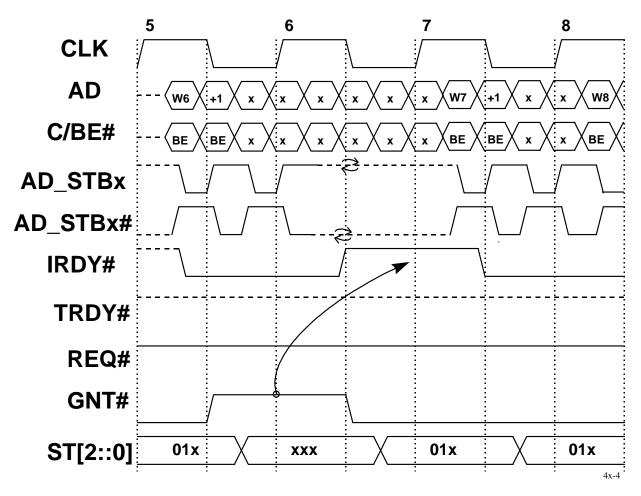

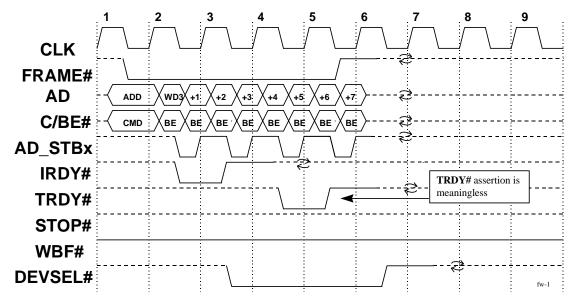

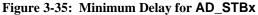

| Figure 3-35:  | Minimum Delay for AD_STBx                                   | . 83 |

| Figure 3-36:  | Maximum Delay for AD_STBx                                   | . 84 |

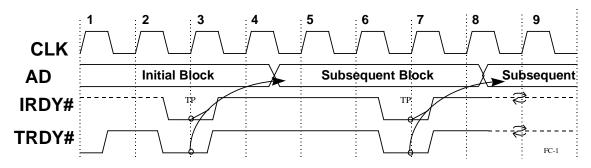

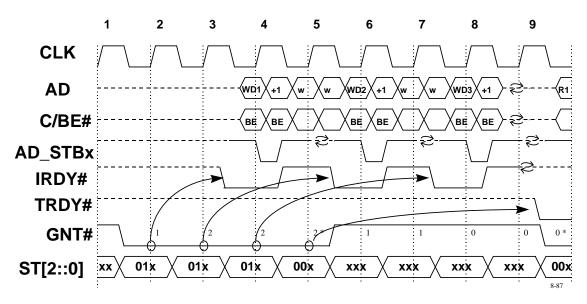

| Figure 3-37:  | Transaction with Subsequent Block                           | . 85 |

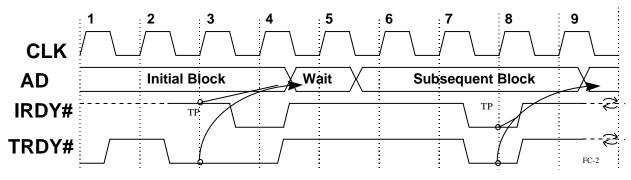

| Figure 3-38:  | Master Delays Data One Clock                                | . 86 |

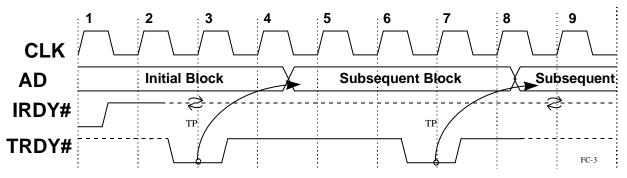

| Figure 3-39:  | Target Delays Subsequent Block                              | . 86 |

| Figure 3-40:  | Target Stops Transaction After Second Block                 | . 87 |

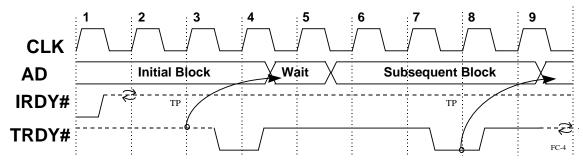

| Figure 3-41:  | Target Delays and Then Stops Transaction After Second Block | . 88 |

| Figure 3-42:  | Target Stop Transaction After First Block                   | . 89 |

| Figure 3-43:  | Target Delays and Then Stops Transaction After First Block  | . 90 |

| Figure 3-44 7 | Target-Abort                                                | .91  |

| Figure 3-45 N | Master-Abort                                                | .92  |

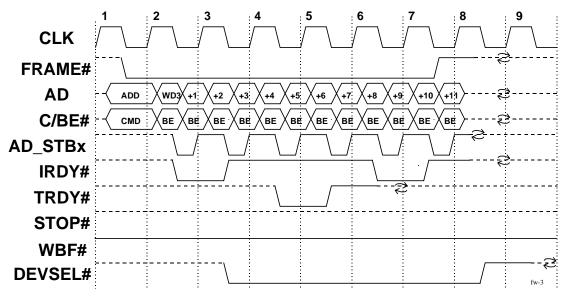

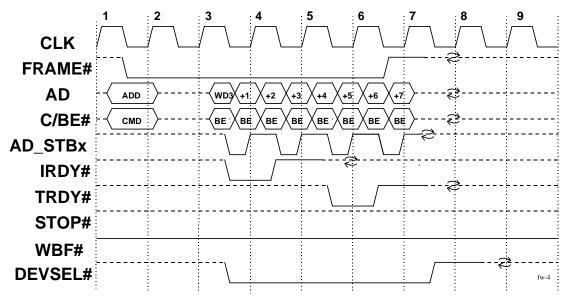

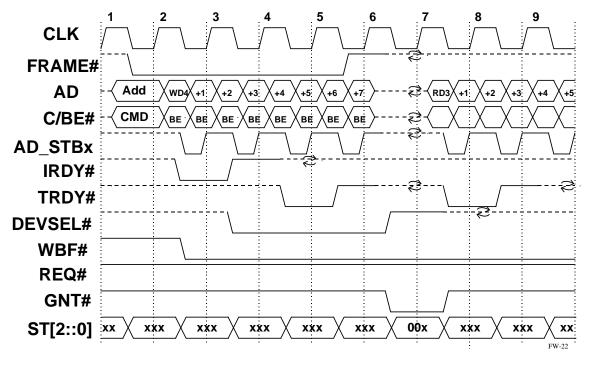

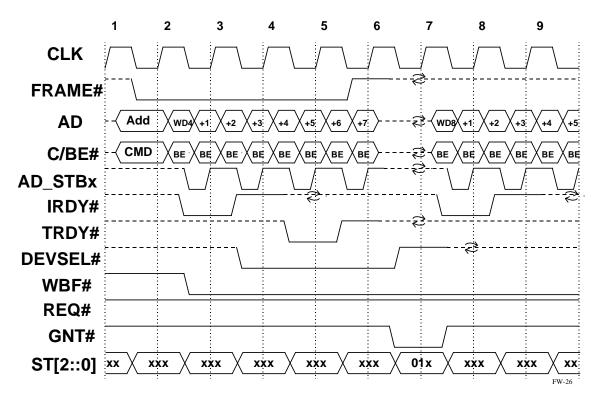

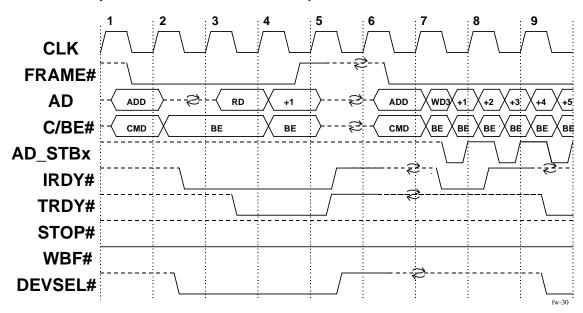

| Figure 3-46:  | Back-to-Back Transaction with Turn-around Cycle             | . 94 |

| Figure 3-47:  | Fast Back-to-Back Transaction                               | .95  |

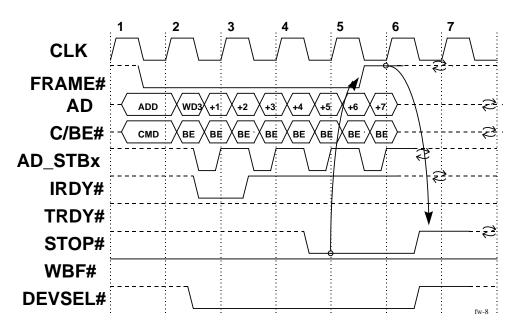

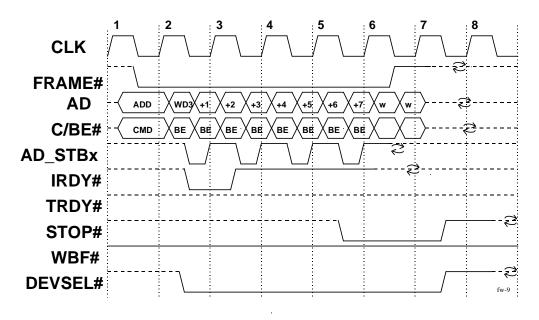

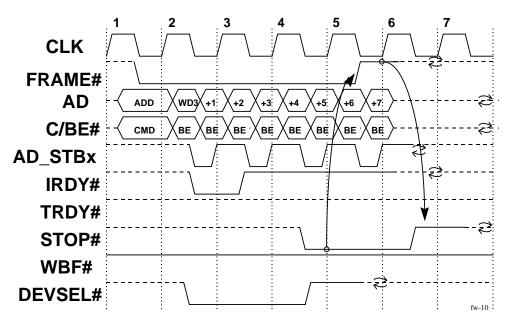

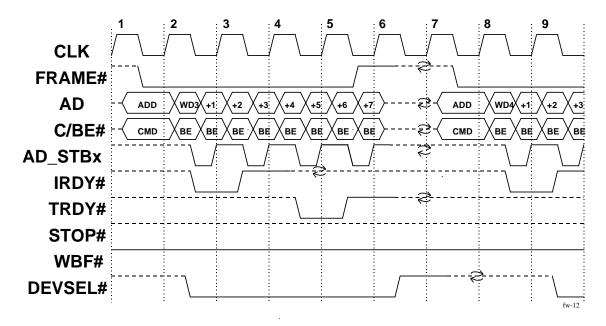

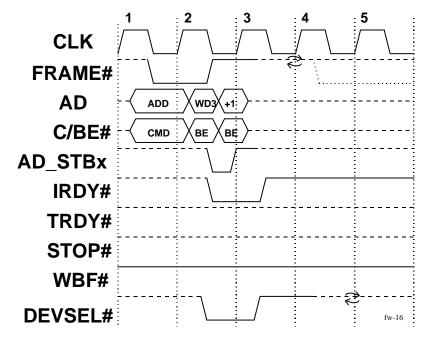

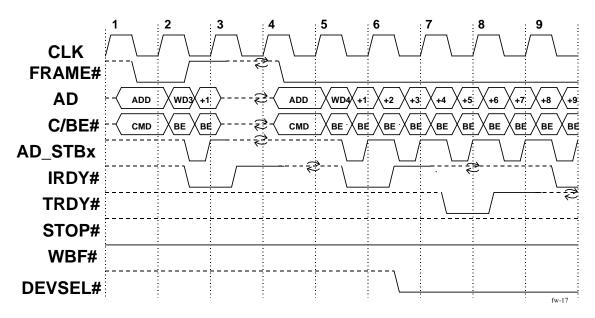

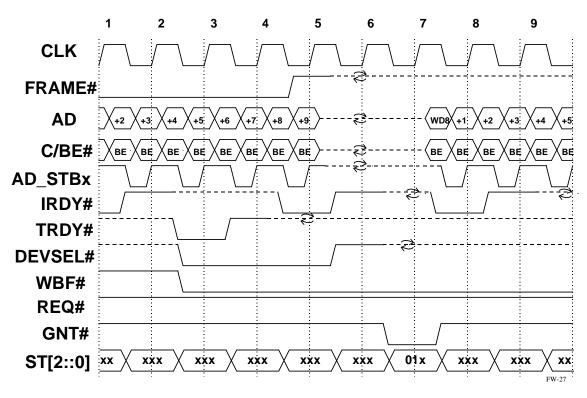

| Figure 3-48:  | WBF# Asserted Prevents Second Transaction                   | .96  |

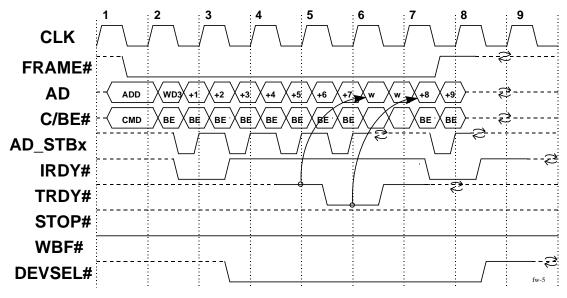

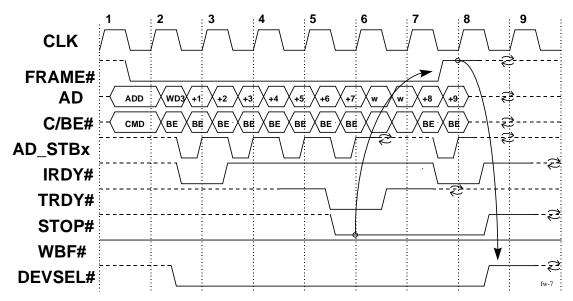

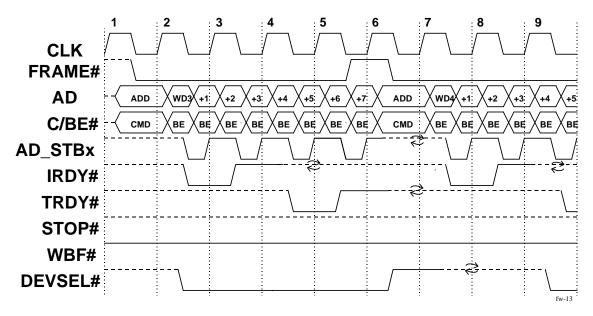

| Figure 3-49:  | Second Transaction Prevented Because WBF# is Asserted       | . 97 |

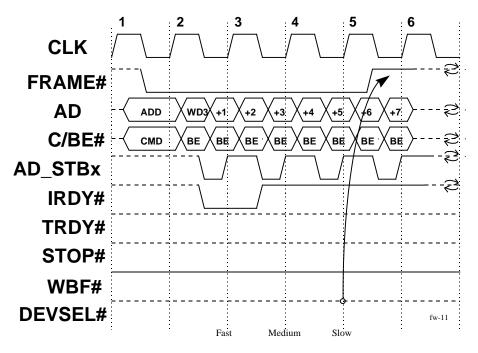

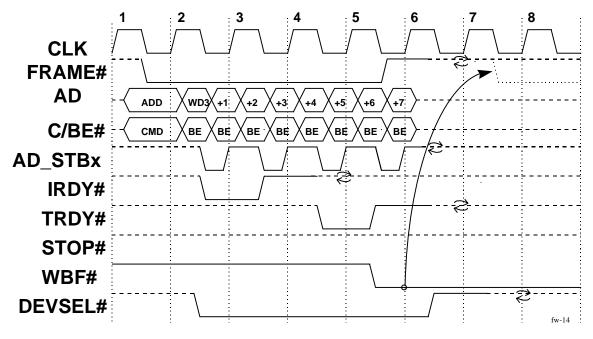

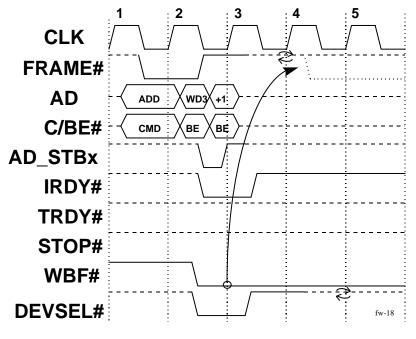

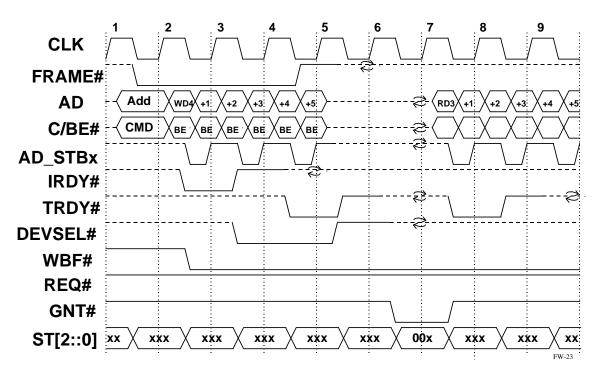

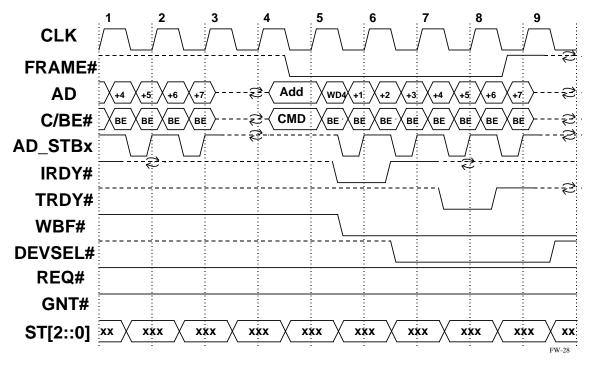

| Figure 3-50:  | Relationship of DEVSEL# and Short Transaction               | . 98 |

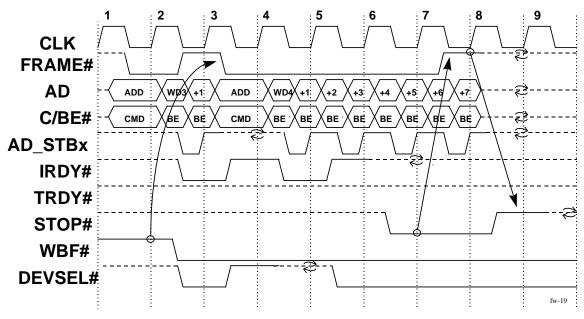

| Figure 3-51:  | Suppression of DEVSEL# on a Short Transaction               | . 99 |

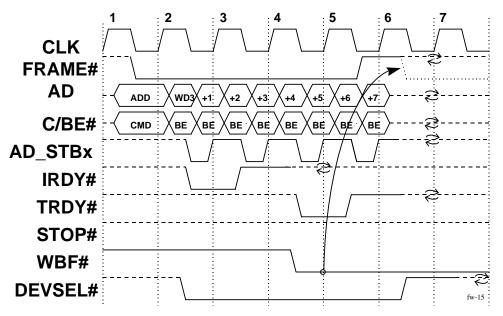

| Figure 3-52:  | WBF# Asserted When First Transaction is Short               | . 99 |

| Figure 3-53:  | Back-to-Back Transaction When First Transaction is Short    | 100  |

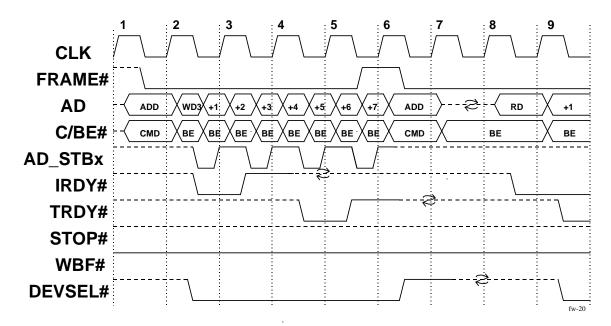

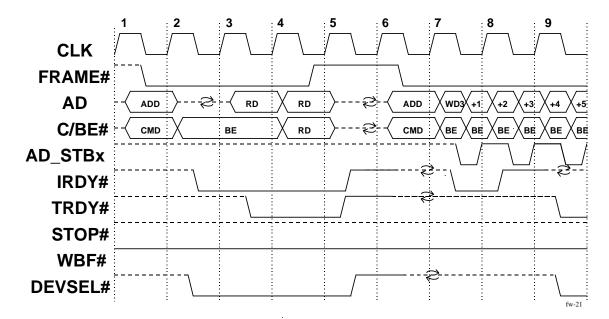

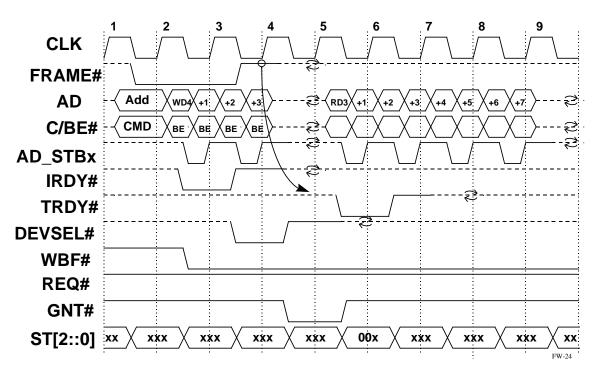

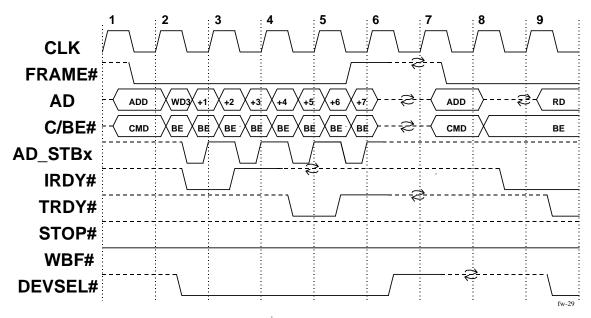

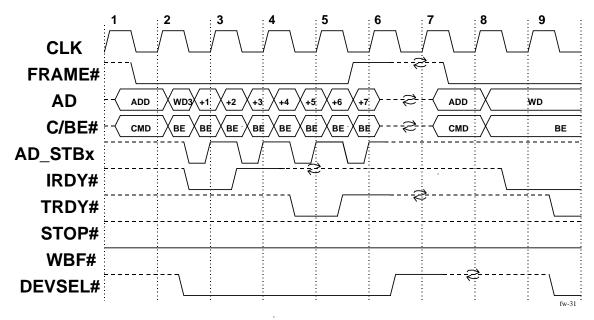

| Figure 3-54:  | FW Followed by PCI Read by Corelogic                        | 101  |

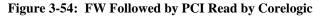

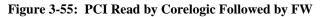

| Figure 3-55:  | PCI Read by Corelogic Followed by FW                        | 102  |

| Figure 3-56:  | FW Followed by an A.G.P. Read Data                          | 103  |

| Figure 3-57:  | Two Dead Clocks Between FW and an A.G.P. Read Data          | 104  |

| Figure 3-58:  | Short FW Followed by an A.G.P. Read Data                    | 105  |

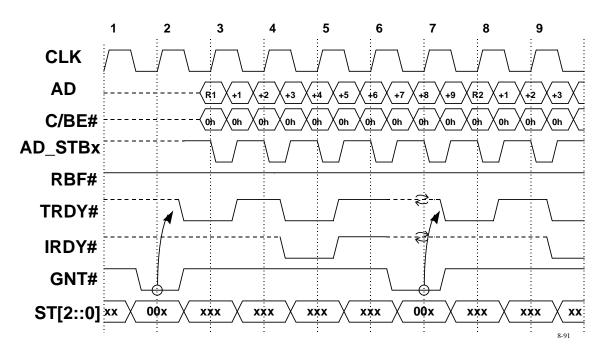

| Figure 3-59:  | A.G.P. Read Followed by an FW Transaction                   | 106  |

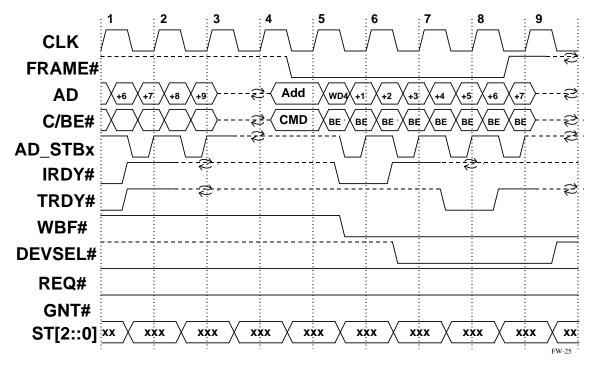

| Figure 3-60: | FW Followed by an A.G.P. Write Data                                   | 107 |

|--------------|-----------------------------------------------------------------------|-----|

| Figure 3-61: | Long FW Followed by an A.G.P. Write Data                              | 108 |

| Figure 3-62: | A.G.P. Write Followed by FW                                           | 109 |

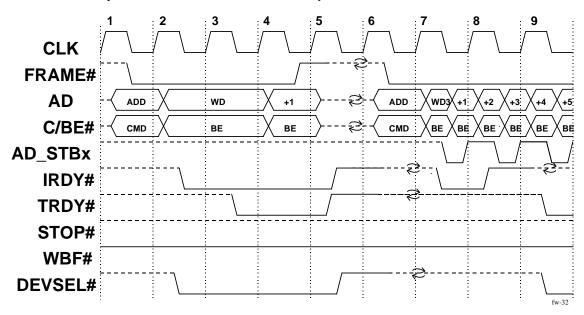

| Figure 3-63: | FW Followed by Graphics PCI Master Read                               | 110 |

| Figure 3-64: | Graphics PCI Master Read Followed by FW                               | 111 |

| Figure 3-65: | FW Followed by Graphics PCI Master Write                              | 112 |

| Figure 3-66: | Graphics PCI Master Write Followed by FW                              | 113 |

| Figure 3-67: | FW Followed by an A.G.P. Request                                      | 114 |

| Figure 3-68: | Request Enqueued Followed by an FW Transaction                        | 115 |

| Figure 3-69: | Request Followed by an FW Transaction                                 | 116 |

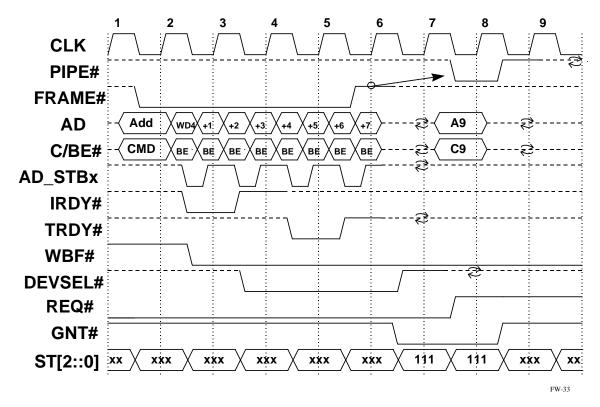

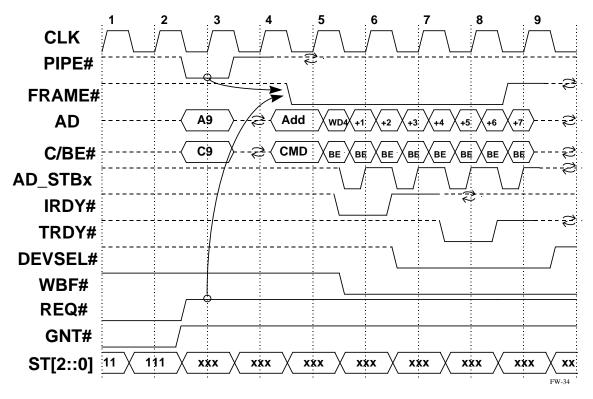

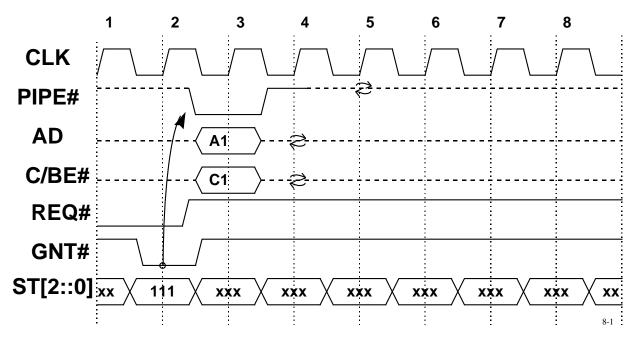

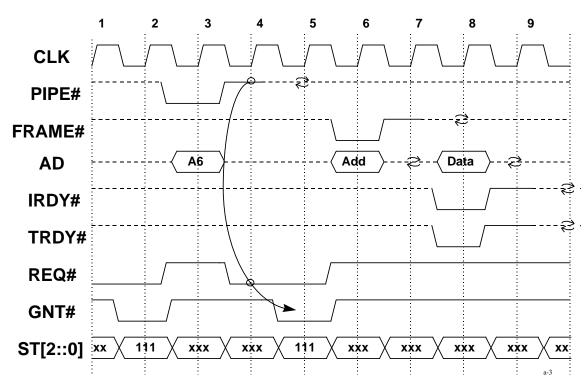

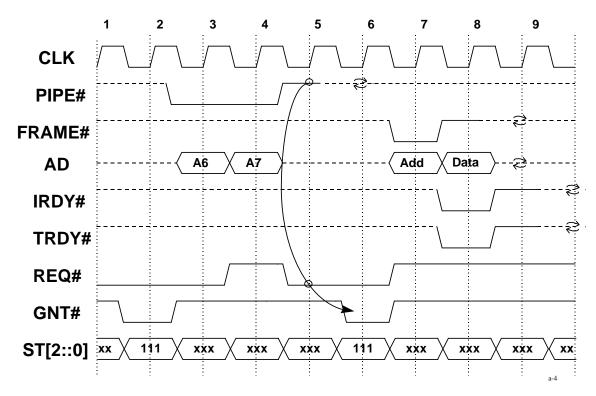

| Figure 3-70: | Single Address - No Delay by Master                                   | 118 |

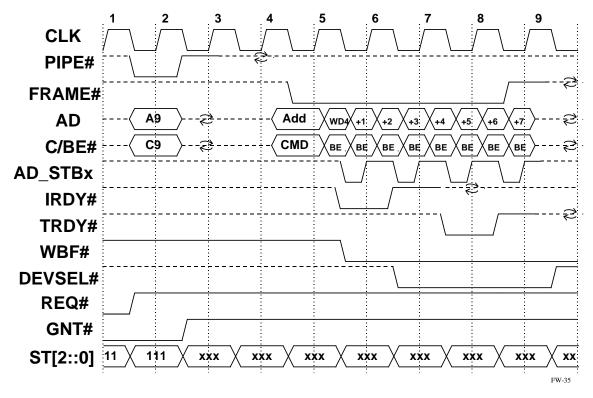

| Figure 3-71: | Single Address - Maximum Delay by Master                              | 119 |

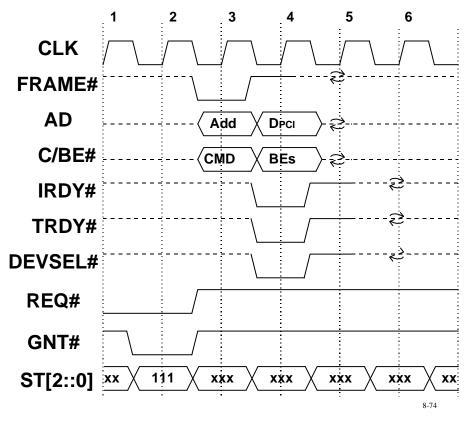

| Figure 3-72: | PCI Write Transaction on the A.G.P. Interface                         | 120 |

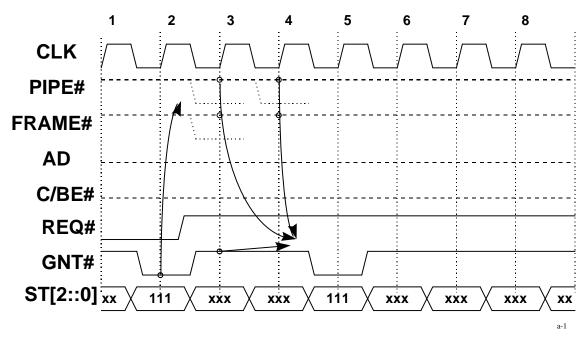

| Figure 3-73: | Arbiter Removes Grant - Master Does Not Start                         | 121 |

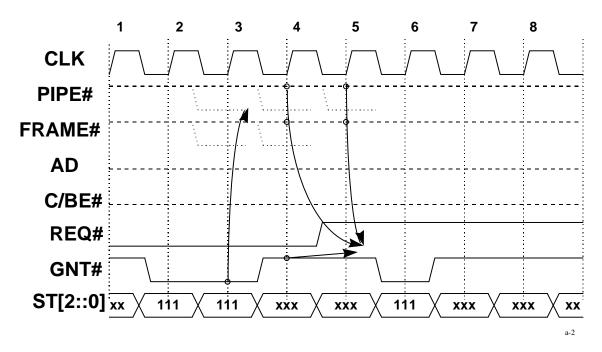

| Figure 3-74: | Arbiter Removes Grant Later - Master Still Does Not Start             | 122 |

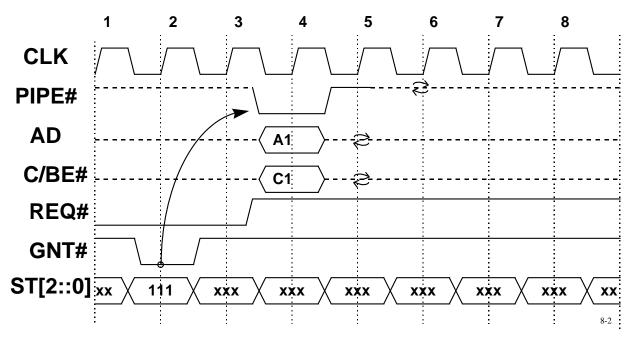

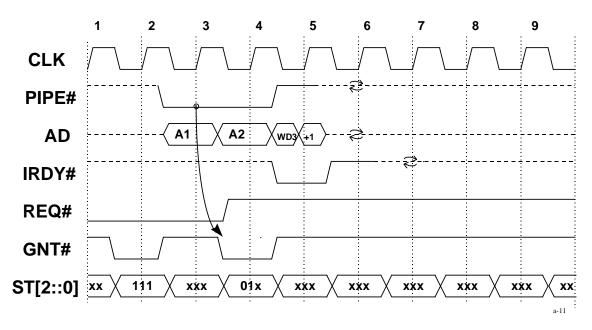

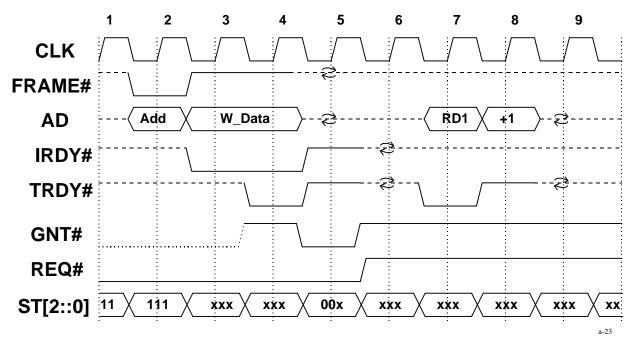

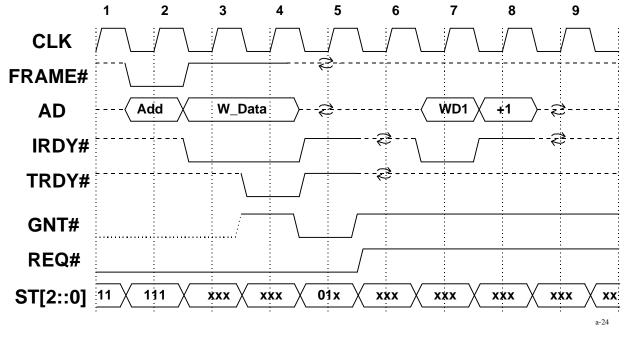

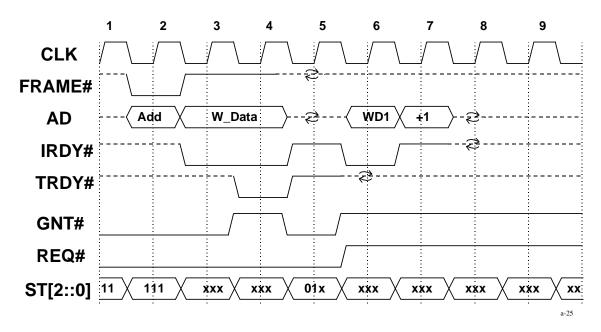

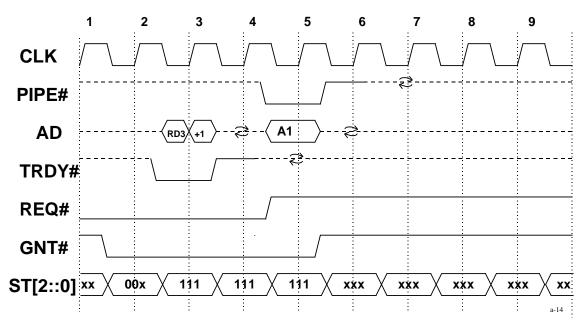

| Figure 3-75: | PIPE# Followed by an A.G.P. Master's PCI Read Transaction             | 125 |

| Figure 3-76: | Double Phase PIPE# Followed by an A.G.P. Master PCI Write Transaction | 126 |

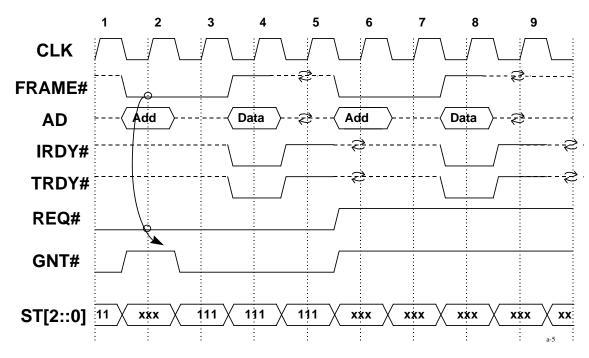

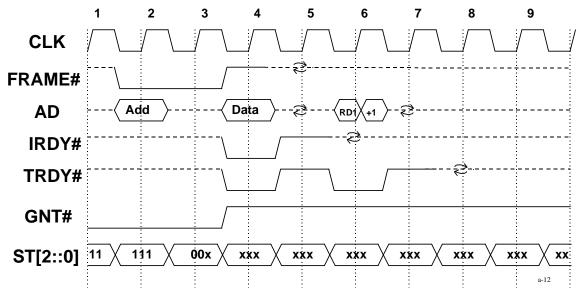

| Figure 3-77: | Back-to-Back PCI Read Transactions                                    | 127 |

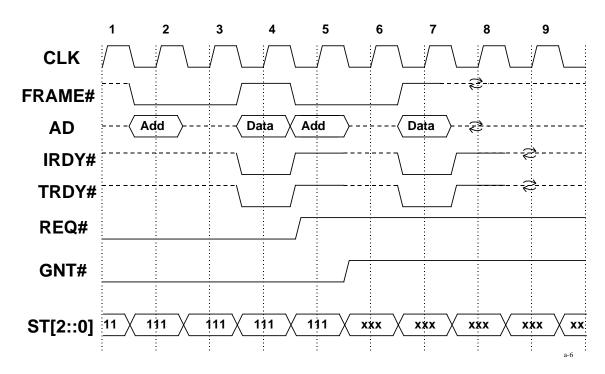

| Figure 3-78: | Fast Back-to-Back PCI Write Transactions                              | 128 |

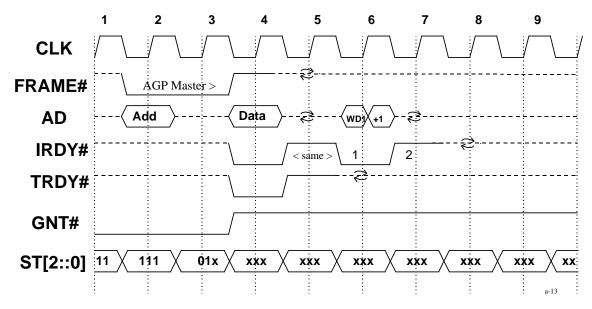

| Figure 3-79: | PCI Read Transaction Followed by PIPE#                                | 129 |

| Figure 3-80: | PCI Write Transaction Followed by PIPE#                               | 130 |

| Figure 3-81: | PIPE# Followed by Read Data                                           | 131 |

| Figure 3-82: | PIPE# Followed by Write Data                                          | 131 |

| Figure 3-83: | Double Phase PIPE# Followed by Write Data                             | 132 |

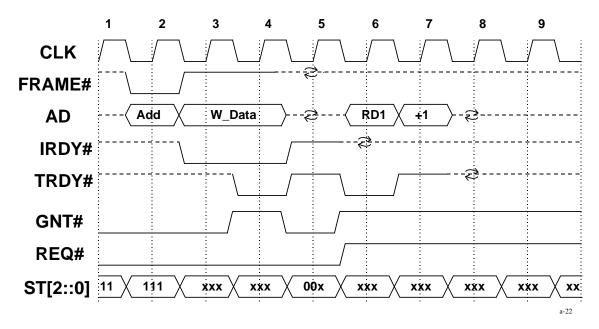

| Figure 3-84: | Master's PCI Read Transaction Followed by Read Data                   | 133 |

| Figure 3-85: | A.G.P. Master's PCI Read Transaction Followed by Write Data           | 134 |

| Figure 3-86: | A.G.P. Master's PCI Write Followed by Read Data                       | 135 |

| Figure 3-87: | Corelogic's PCI Write Followed by Read Data                           | 135 |

| Figure 3-88: | Corelogic's PCI Write Transaction Followed by Write Data              | 136 |

| Figure 3-89: | A.G.P. Master's PCI Write Transaction Followed by Write Data          | 137 |

| Figure 3-90: | Single Read Data Followed by PIPE#                                    | 138 |

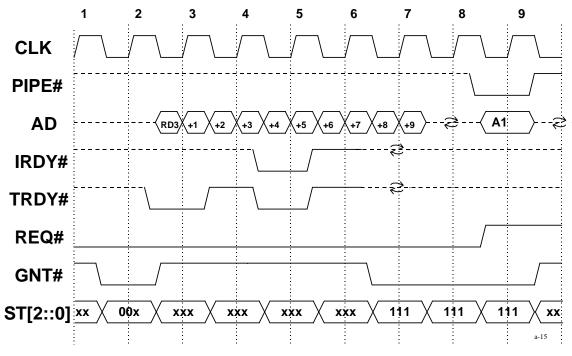

| Figure 3-91: | Burst Read Data Followed by PIPE#                                     | 139 |

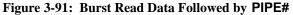

| Figure 3-92: | Single Write Data Followed by PIPE#                                   | 140 |

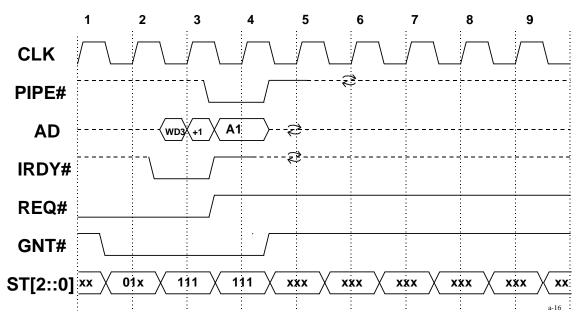

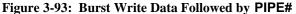

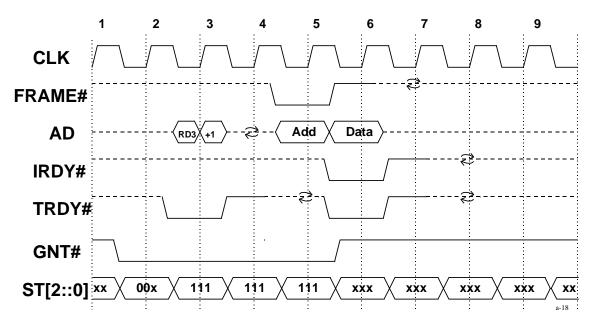

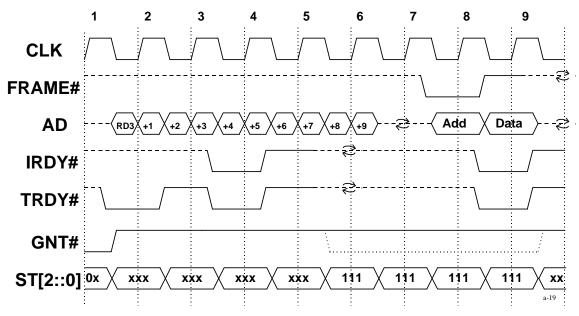

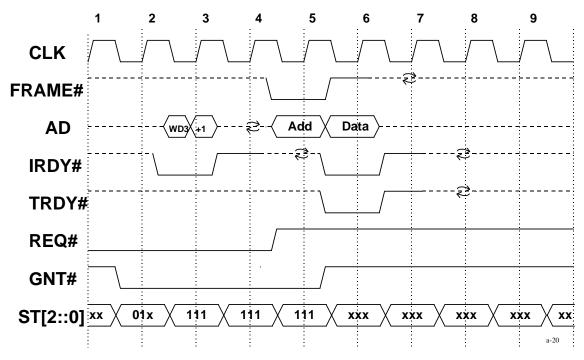

| Figure 3-93: Burst Write Data Followed by PIPE#                              | 141 |

|------------------------------------------------------------------------------|-----|

| Figure 3-94: Single Read Data Followed by A.G.P. Master's PCI Transaction    | 141 |

| Figure 3-95: Burst Read Data Followed by A.G.P. Corelogic's PCI Transaction  | 142 |

| Figure 3-96: Single Write Data Followed by A.G.P. Master's PCI Transaction   | 143 |

| Figure 3-97: Burst Write Data Followed by an A.G.P. Master's PCI Transaction | 144 |

| Figure 3-98: Back-to-Back Read Data                                          | 145 |

| Figure 3-99: GNT# Assertion for 16, 8, and then 16 Byte Read Transfers       | 145 |

| Figure 3-100: GNT# Assertion for Next Read Data After Long Data Transfer     | 146 |

| Figure 3-101: LP GNT# Pipelining Stopped While RBF# is Asserted              | 146 |

| Figure 3-102: GNT# Assertion for Back-to-Back Write Data Transfers           | 147 |

| Figure 3-103: Back-to-Back GNT# with Delay on Initial Transfer               |     |

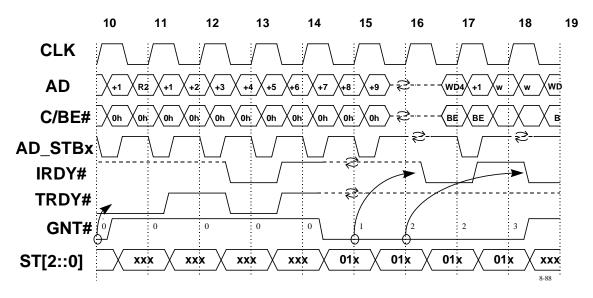

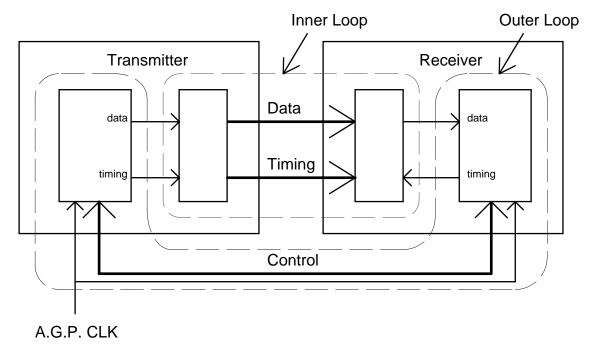

| Figure 3-104: Pipelined GNT#s - Read and Writes (Part 1)                     | 149 |

| Figure 3-105: Pipelined GNT#s - Read and Writes (Part 2)                     | 149 |

| Figure 3-106: A.G.P.Write Followed by a Read                                 |     |

| Figure 4-1: 2X/4X Mode Time Domains                                          |     |

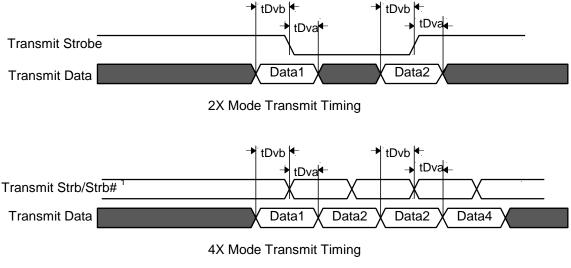

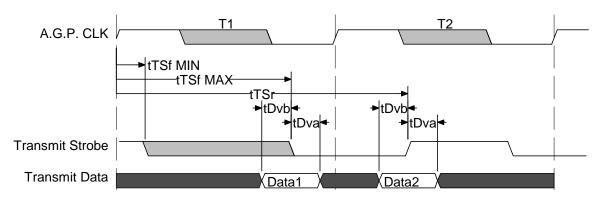

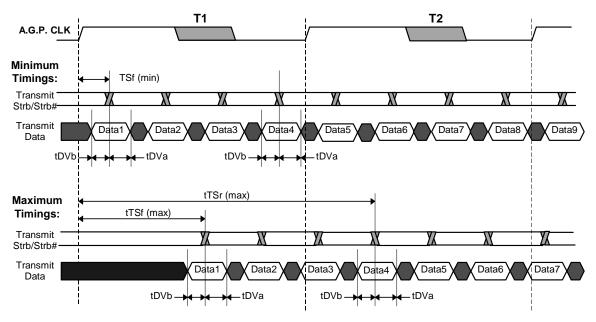

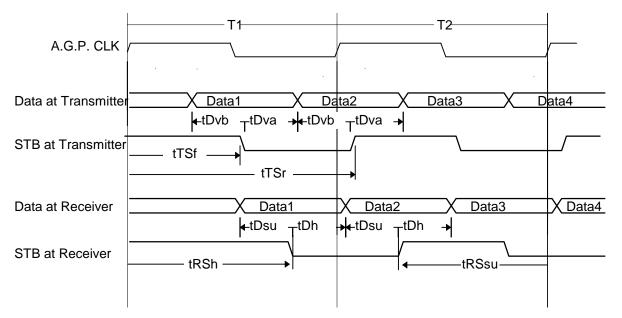

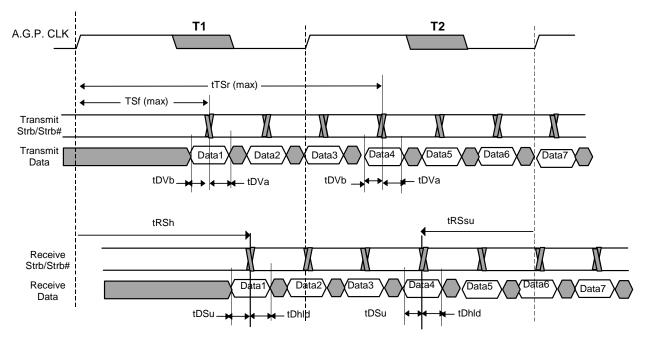

| Figure 4-2: Mode Transmit Strobe/Data Timings                                | 156 |

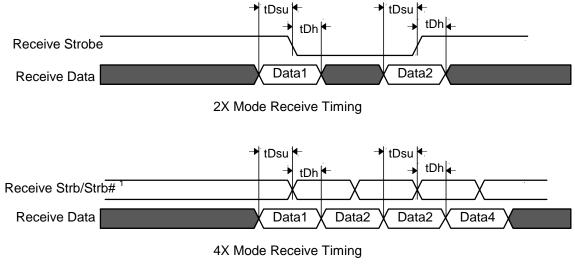

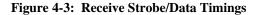

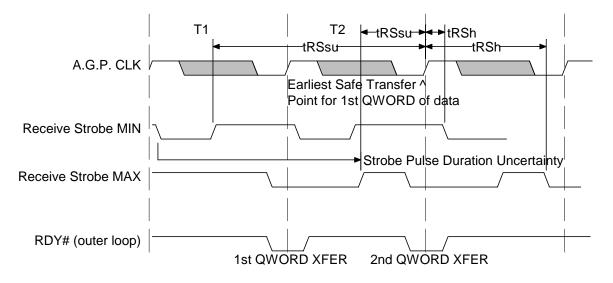

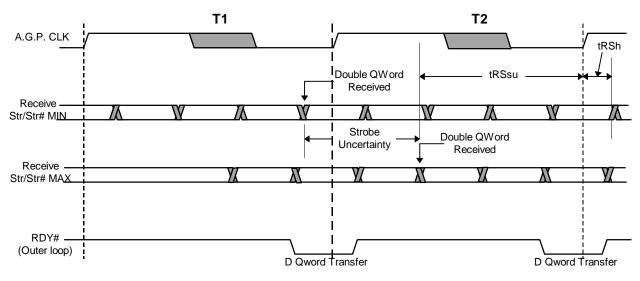

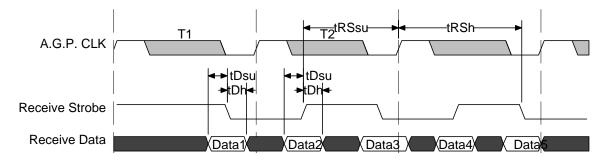

| Figure 4-3: Receive Strobe/Data Timings                                      | 157 |

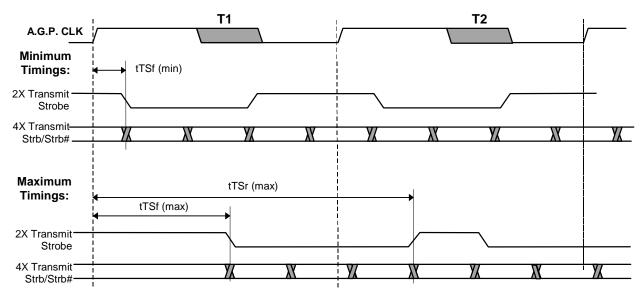

| Figure 4-4: Transmit Strobe/Clock Timings                                    | 157 |

| Figure 4-5: Composite 2X Mode Transmit Timings                               |     |

| Figure 4-6: Composite 4X Mode Transmit Timings                               |     |

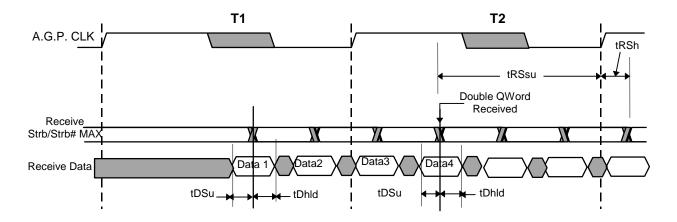

| Figure 4-7: 2X Mode Receiver Inner to Outer Loop Transfer Timing             | 159 |

| Figure 4-8: 4X Mode Receiver Inner to Outer Loop Transfer Timing             |     |

| Figure 4-9: 2X Composite Receive Timings                                     |     |

| Figure 4-10: 4X Composite Receive Timings                                    | 161 |

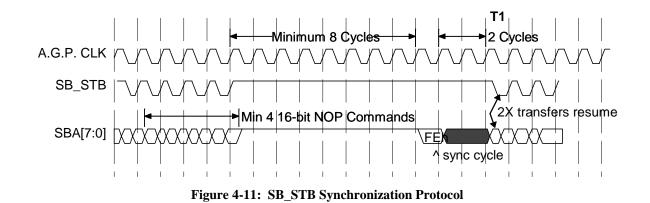

| Figure 4-11: SB_STB Synchronization Protocol                                 |     |

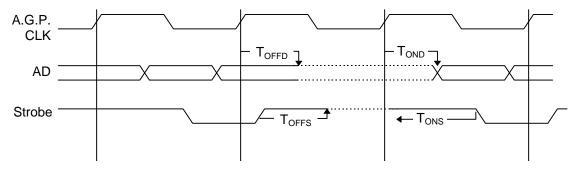

| Figure 4-12: A.G.P. 1X Timing Diagram                                        | 167 |

| Figure 4-13: A.G.P. 133 Timing Diagram                                       | 169 |

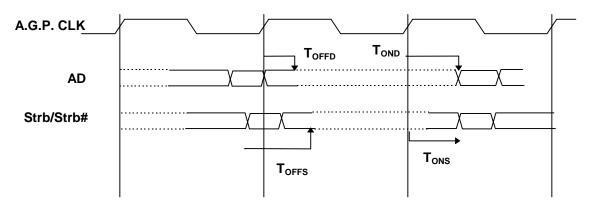

| Figure 4-14: Strobe/Data Turnaround Timings                                  |     |

| Figure 4-15: 4X Mode Timing Diagram                                          | 171 |

| Figure 4-16: 4X Mode Strobe/Data Turnaround Timings                          | 171 |

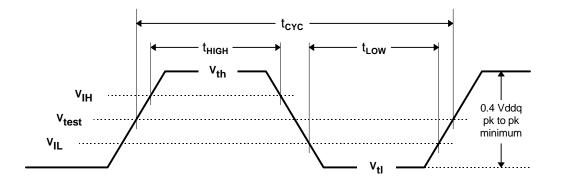

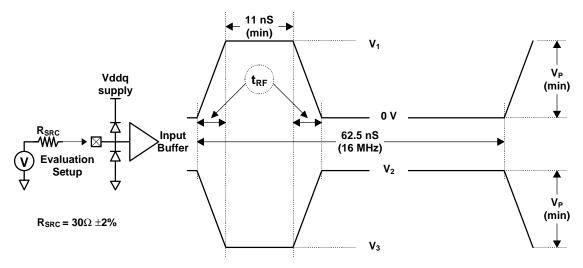

| Figure 4-17: Clock Input Measurement Conditions                              |     |

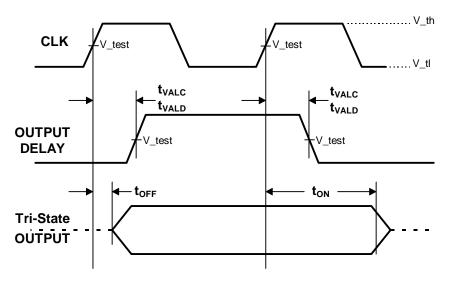

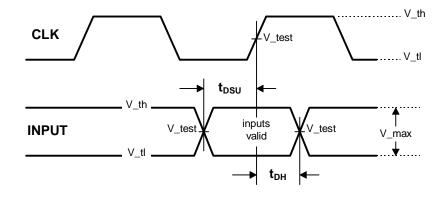

| Figure 4-18: Output Timing Measurement Conditions                            |     |

| Figure 4-19: Input Timing Measurement Conditions                             |     |

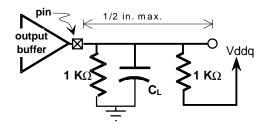

| Figure 4-20: Load for Testing Output Timings                                             |     |

|------------------------------------------------------------------------------------------|-----|

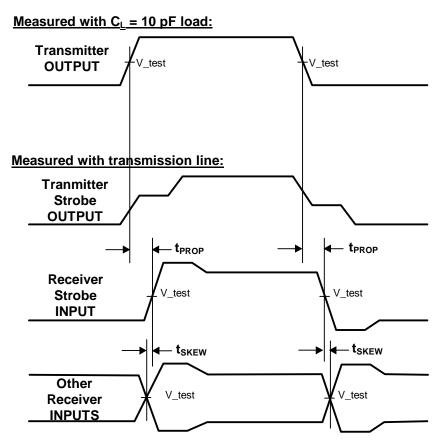

| Figure 4-21: Flight Time and Skew Measurement                                            | 174 |

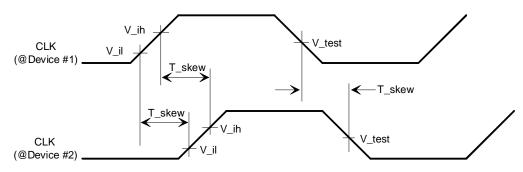

| Figure 4-22: Clock Skew Diagram                                                          | 176 |

| Figure 4-23: Maximum AC Waveforms for A.G.P. Signaling                                   | 179 |

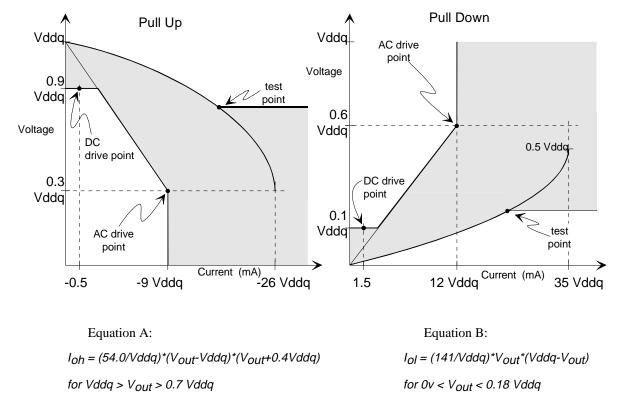

| Figure 4-24: V/I Curves for 3.3 Volt Signaling                                           |     |

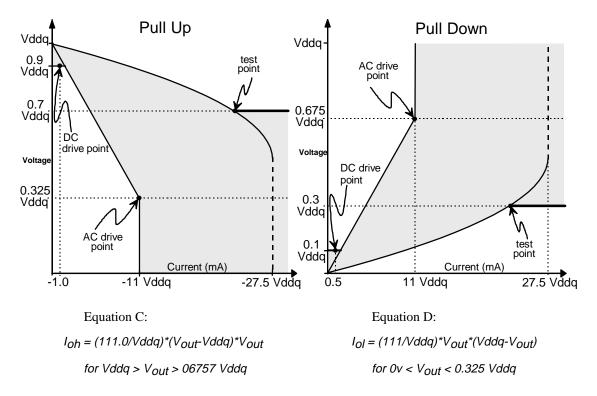

| Figure 4-25: V/I Curves for 1.5 Volt Signaling                                           |     |

| Figure 4-26: Recommended Component Pinout                                                |     |

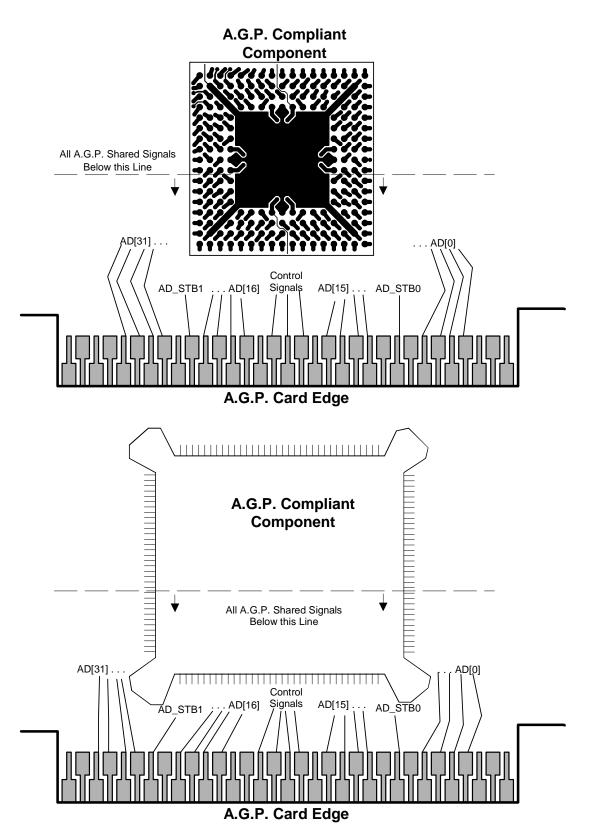

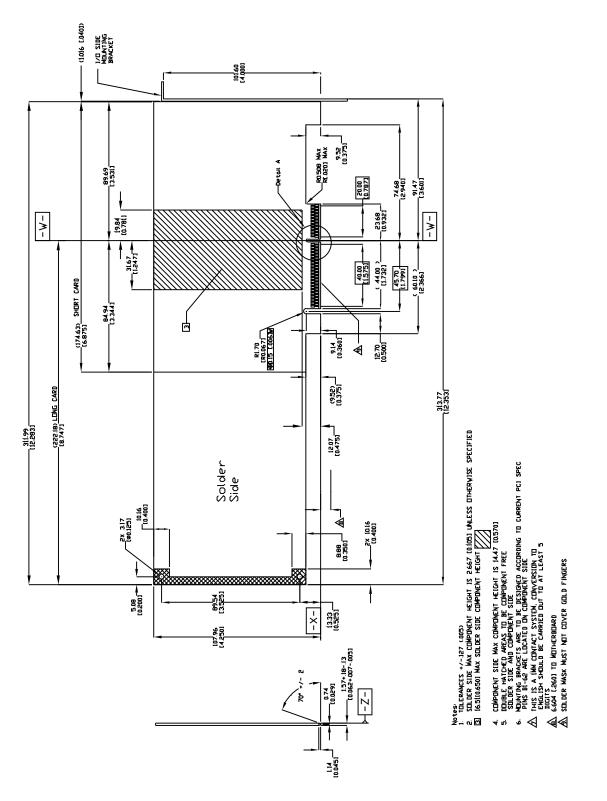

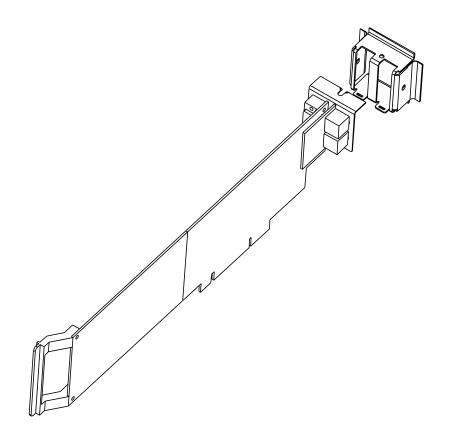

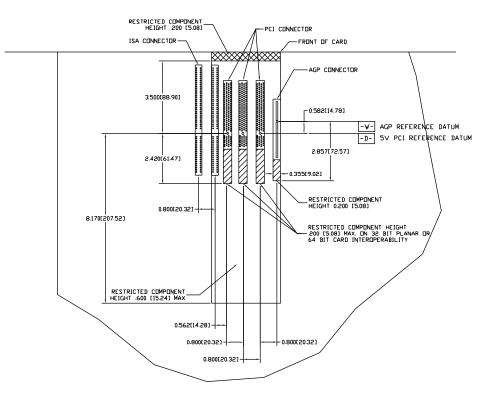

| Figure 5-1: A.G.P. ATX Form Factor Add-in Card                                           | 196 |

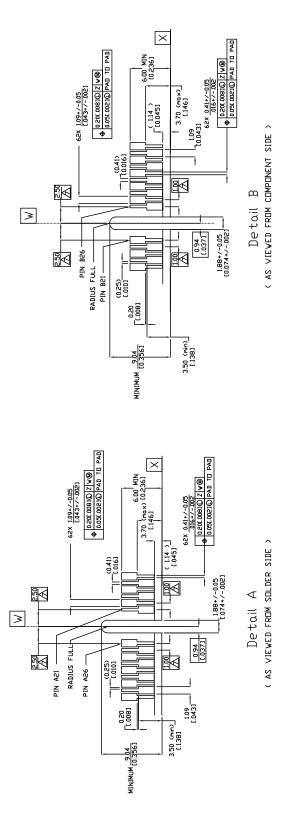

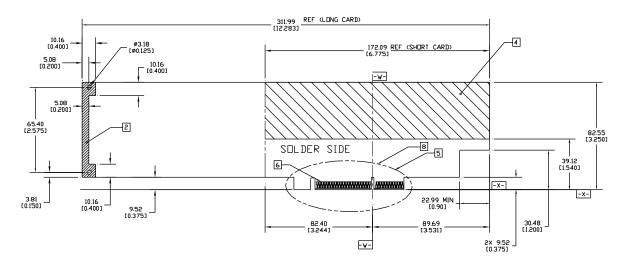

| Figure 5-2: Detail A and B: A.G.P. Card Edge Finger Layout                               | 197 |

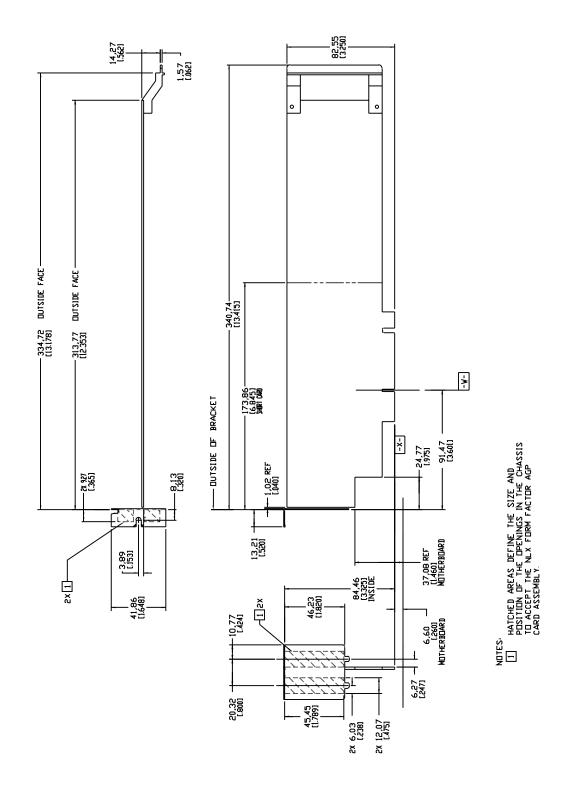

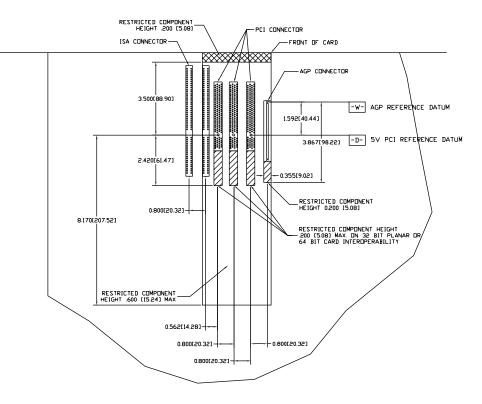

| Figure 5-3: A.G.P. NLX Form Factor Add-in Card                                           |     |

| Figure 5-4: A.G.P. NLX Factor Add-in Card Comprehensive                                  | 199 |

| Figure 5-5: A.G.P. NLX Form Factor Card Detail                                           |     |

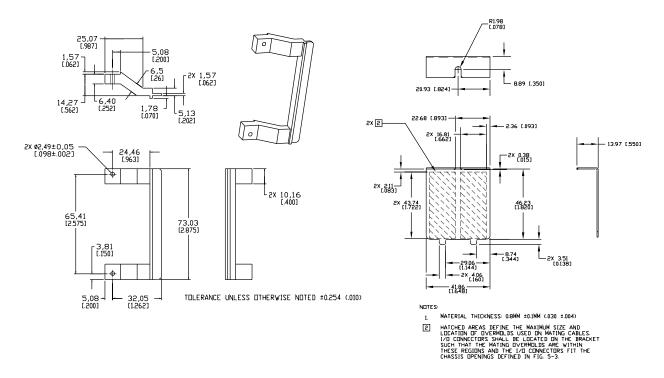

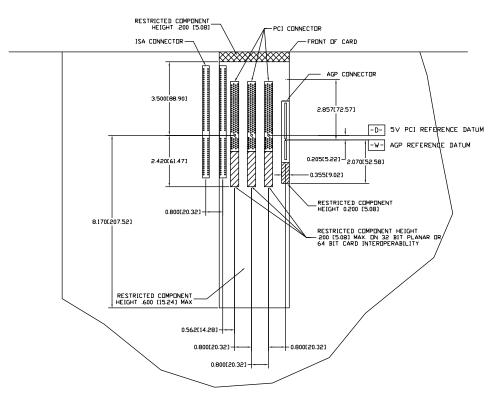

| Figure 5-6: A.G.P. NLX Form Factor Add-in Card Reference Bracket Details                 |     |

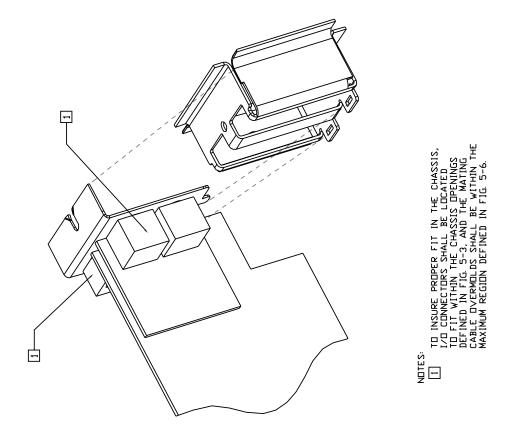

| Figure 5-7: A.G.P. NLX Form Factor I/O Bracket and Chassis Interaction                   |     |

| Figure 5-8: A.G.P. Card Edge Connector Bevel                                             |     |

| Figure 5-9A: A.G.P. 3.3 Volt Connector Footprint and Layout Dimensions                   |     |

| Figure 5-9B: A.G.P. 3.3 Volt Connector Footprint and Layout Dimensions                   |     |

| Figure 5-10A: A.G.P. Universal Connector Footprint and Layout Dimensions                 |     |

| Figure 5-10B: A.G.P. Universal Connector Footprint and Layout Dimensions                 |     |

| Figure 5-11A: A.G.P. Add-in Card 1.5 Volt Connector Footprint and Layout Dimensions      | 211 |

| Figure 5-11B: A.G.P. Add-in Card 1.5 Volt Connector Footprint and Layout Dimensions      | 212 |

| Figure 5-12 Typical ATX 3.3 Volt Connector Implementation                                |     |

| Figure 5-13: Typical ATX Universal Connector Implementation                              | 214 |

| Figure 5-14: Typical ATX 1.5 Volt Connector Implementation                               | 214 |

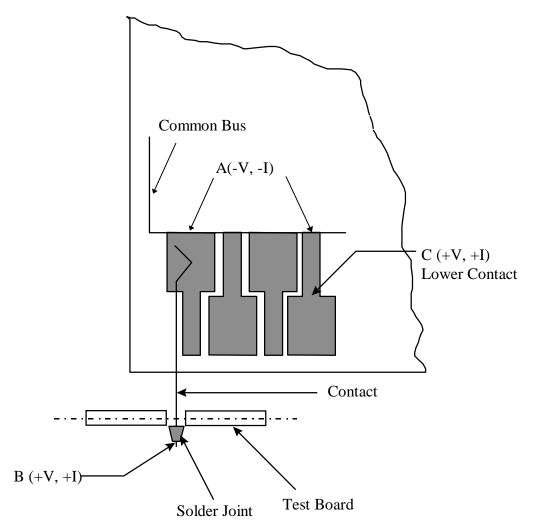

| Figure 5-15: Bulk Resistance Measurement                                                 | 219 |

| Figure 5-16. Test Structure for Impedance, Propagation Delay, and Crosstalk Measurements |     |

| Figure 6-1: Configuration View of an A.G.P. Target                                       |     |

| Figure 6-2: Location of A.G.P. Capabilities                                              | 231 |

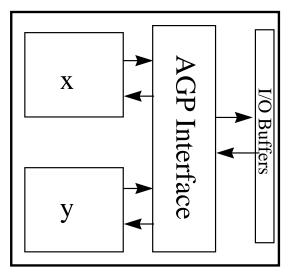

| Figure 6-3: PCI Device Block                                                             | 236 |

| Figure 6-4: A.G.P. Block                                                                 | 237 |

## Tables

| Table 3-1: A.G.P. Requests                                            |     |

|-----------------------------------------------------------------------|-----|

| Table 3-2: A.G.P. Flow Control                                        |     |

| Table 3-3: A.G.P. Status Signals                                      |     |

| Table 3-4: A.G.P. Clock List                                          |     |

| Table 3-5: USB Signals                                                |     |

| Table 3-6: Power Management on A.G.P.                                 |     |

| Table 3-7: Special Interface Signals                                  |     |

| Table 3-8: PCI Signals in Relation to A.G.P.                          |     |

| Table 3-9: Summary of Interfaces Based on Function and Agent          |     |

| Table 3-10: Summary of PCI Signals Based on Function and Agent        |     |

| Table 3-11: Summary of A.G.P. Signals Based on Function and Agent     |     |

| Table 3-12: A.G.P. Bus Commands                                       |     |

| Table 3-13: SBA Port Encoding                                         |     |

| Table 3-14: SBA Signals                                               | 53  |

| Table 3-15: A.G.P. Master Flow Control Conditions                     |     |

| Table 3-16: A.G.P. Target Flow Control Conditions                     | 61  |

| Table 3-17: Data Buffering for 2x Transfers                           |     |

| Table 3-18: Data Buffering for 4x Transfers                           |     |

| Table 3-19: Back to Back Transactions                                 |     |

| Table 3-20: A.G.P. Arbitration Rules                                  | 117 |

| Table 3-21: Current/Next AD Activity                                  |     |

| Table 4-1: Allowed Transfer Mode Signaling Levels                     |     |

| Table 4-2: DC Specifications for A.G.P. 1X Signaling at 3.3 Volts     |     |

| Table 4-3: DC Specifications for A.G.P. 1X Signaling at 1.5 volts.    |     |

| Table 4-4: DC Specifications for 2X Mode Only at 3.3 volts Signaling  |     |

| Table 4-5: DC Specifications for 2X or 4X Mode at 1.5 volts Signaling | 164 |

| Table 4-6: A.G.P. 1X AC Timing Parameters                             | 166 |

| Table 4-7:   A.G.P. 2X AC Timing Parameters                           |     |

| Table 4-8: A.G.P. 4X AC Timing Parameters                             |     |

| Table 4-9: Measurement and Test Condition Parameters                  |     |

| Table 4-10:    Clock Skew Parameters, All Transfer Rates         |  |

|------------------------------------------------------------------|--|

| Table 4-11: Motherboard / Add-in Card Interoperability           |  |

| Table 4-12: Pull-up Resistor Values                              |  |

| Table 4-13: Parameters for Maximum AC A.G.P. Signaling Waveforms |  |

| Table 4-14: Add-in Card Power Supply Limits                      |  |

| Table 4-15: Signal Integrity Requirements <sup>1</sup>           |  |

| Table 4-16: AC Specifications for A.G.P. 3.3 Volt Signaling      |  |

| Table 4-17: AC Specifications for A.G.P. 1.5 Volt Signaling      |  |

| Table 4-18: 1X / 2X Mode System Timing Summary                   |  |

| Table 4-19: 1X / 2X Mode Interconnect Delay Summary              |  |

| Table 4-20:    1X / 2X Mode Motherboard Interconnect Delays      |  |

| Table 4-21: 1X / 2X Mode Add-in Card Interconnect Delays         |  |

| Table 5-1: Thermal Specification for Add-in Cards                |  |

| Table 5-2: A.G.P. Motherboard Connector Pinout                   |  |

| Table 5-3: Qualification Test                                    |  |

| Table 6-1: Commands Supported by Each Port                       |  |

| Table 6-2: A.G.P. Options                                        |  |

# 1. Introduction

The Accelerated Graphics Port (AGP or A.G.P.) is a high performance, component level interconnect targeted at 3D graphical display applications and is based on a set of performance extensions or enhancements to the PCI bus. This document specifies the A.G.P. interface, and provides some design suggestions for effectively using it in high performance 3D graphics display applications.

## 1.1 Motivation

In general, 3D rendering has a voracious appetite for memory bandwidth, and continues to put upward pressure on memory footprint as well. As 3D hardware and software become more pervasive, these two trends are likely to accelerate, requiring high speed access to ever larger amounts of memory, thus raising the bill of material costs for 3D enabled platforms. Containing these costs while enabling performance improvements is the primary motivation for the A.G.P. By providing up to an order of magnitude bandwidth improvement between the graphics accelerator and system memory, some of the 3D rendering data structures may be effectively shifted into main memory, relieving the pressure to increase the cost of the local graphics memory.

Texture data are the first structures targeted for shifting to system memory for four reasons:

- 1. Textures are generally read only, and, therefore, do not have special access ordering or coherency problems.

- 2. Shifting textures balances the bandwidth load between system memory and local graphics memory, since a well cached host processor has much lower memory bandwidth requirements than does a 3D rendering engine. Texture access comprises perhaps the largest single component of rendering memory bandwidth (compared with rendering, display and Z buffers): so avoiding loading or caching textures in graphics local memory saves not only this component of local memory bandwidth, but also the bandwidth necessary to load the texture store in the first place. Furthermore, this data must pass through main memory anyway as it is loaded from a mass store device.

- 3. Texture size is dependent upon application quality rather than on display resolution, and, therefore, subject to the greatest pressure for growth.

- 4. Texture data is not persistent; it resides in memory only for the duration of the application, so any system memory spent on texture storage can be returned to the free memory heap when the application concludes (unlike display buffers which remain in persistent use).

Other data structures may be moved to main memory but texture data is the biggest win.

Reducing costs by moving graphics data to main memory is the primary motivation for the A.G.P., which is designed to provide a smooth, incremental transition for today's PCI based graphics vendors as they develop higher performance components in the future.

## 1.2 Relationship to PCI

The A.G.P. interface specification uses the 66 MHz PCI (*PCI Local Bus Specification*) specification as an operational baseline, and provides four significant performance extensions or enhancements to the PCI specification which are intended to optimize the A.G.P. for high performance 3D graphics applications. These A.G.P. extensions are NOT described in, or required by, the *PCI Local Bus Specification*. These extensions are:

- Deeply pipelined memory read and write operations, fully hiding memory access latency.

- Demultiplexing of address and data on the bus, allowing almost 100% bus efficiency.

- New AC timing in the 3.3 V electrical specification that provides for one or two data transfers per 66-MHz clock cycle, allowing for real data throughput in excess of 500 MB/s.

- A new low voltage electrical specification that allows four data transfers per 66-MHz clock cycle, providing real data throughput of up to 1 GB/s.

These enhancements are realized through the use of "sideband" signals. The PCI specification has not been modified in any way, and the A.G.P. interface specification has specifically avoided the use of any of the "reserved" fields, encodings, pins, etc., in the PCI specification. The intent is to utilize the PCI design base while providing a range of graphics-oriented performance enhancements with varying complexity/performance tradeoffs available to the component provider.

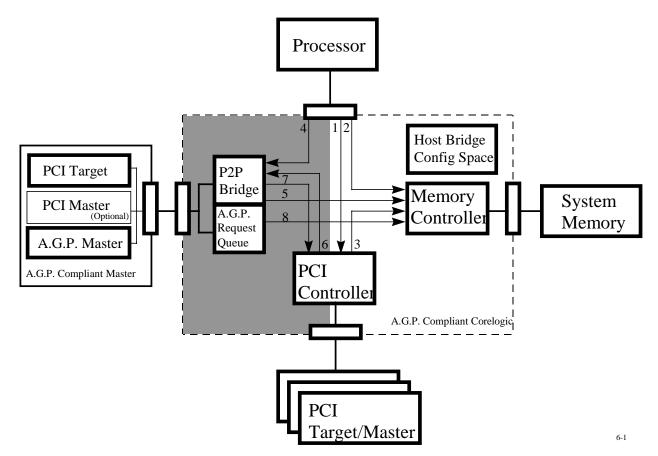

A.G.P. neither replaces nor diminishes the necessity of PCI in the system. This high speed port (A.G.P.) is physically, logically, and electrically independent of the PCI bus. It is an additional connection point in the system, as shown in Figure 1-1. It is intended for the exclusive use of visual display devices; all other I/O devices will remain on the PCI bus. The add-in slot defined for A.G.P. uses a new connector body (for electrical signaling reasons) which is not compatible with the PCI connector; PCI and A.G.P. boards are not mechanically interchangeable.

The A.G.P. interface specification was developed by Intel, independent of the PCI Special Interest Group, and has been neither reviewed nor endorsed by that group. It is intended to encourage innovation in personal computer graphics technology and products.

Figure 1-1: System Block Diagram: A.G.P. and PCI Relationship

## 1.3 Terminology

This revision of the A.G.P. interface specification refers to various devices that are compatible with the A.G.P. interface (for example, masters and targets). The *A.G.P. Interface Specification, Revision 1.0* refers to such devices as A.G.P.-compliant devices or A.G.P.-enabled devices (for example, A.G.P.-compliant masters, A.G.P.-compliant targets, and A.G.P.-enabled masters). This revision of the interface specification simplifies this terminology by using terms such as A.G.P. device, A.G.P. master, and A.G.P. target to refer to devices that are compatible with the A.G.P. interface specification.

# 2. Architectural Context and Scope

This chapter provides an architectural context for the actual specification of the Accelerated Graphics Port (A.G.P. or AGP) interface, hopefully motivating the design and making details easier to understand. It also is intended to set the technical scope of the interface specification in some areas by providing examples of issues beyond the purview of the formal interface specification.

### 2.1 Two Usage Models: "Execute" and "DMA"

There are two primary A.G.P. usage models for 3D rendering that have to do with how data are partitioned and accessed, and the resultant interface data flow characteristics. In the "DMA" model, the primary graphics memory is the local memory associated with the accelerator, referred to as "local frame buffer". 3D structures are stored in system memory, but are not used (or "executed") directly from this memory; rather they are copied to primary (local) memory (the "DMA" operation) to which the rendering engine's address generator makes its references. This implies that the traffic on the A.G.P. tends to be long, sequential transfers, serving the purpose of bulk data transport from system memory to primary graphics (local) memory. This sort of access model is amenable to a linked list of physical addresses provided by software (similar to operation of a disk or network I/O device), and is generally not sensitive to a non-contiguous view of the memory space.

In the "execute" model, the accelerator uses both the local memory and the system memory as primary graphics memory. From the accelerator's perspective, the two memory systems are logically equivalent; any data structure may be allocated in either memory, with performance optimization as the only criteria for selection. In general, structures in system memory space are not copied into the local memory prior to use by the accelerator, but are "executed" in place. This implies that the traffic on the A.G.P. tends to be short, random accesses, which are not amenable to an access model based on software resolved lists of physical addresses. Because the accelerator generates direct references into system memory, a contiguous view of that space is essential; however, since system memory is dynamically allocated in random 4K pages, it is necessary in the "execute" model to provide an address mapping mechanism that maps random 4K pages into a single contiguous, physical address space.

The A.G.P. supports both the "DMA" and "execute" models. However, since a primary motivation of the A.G.P. is to reduce growth pressure on local memory, the "execute" model is the design center. Consistent with that emphasis, this interface specification requires a physical-to-physical address remapping mechanism which insures the graphics accelerator (an A.G.P. master) will have a contiguous view of graphics data structures dynamically allocated in system memory.

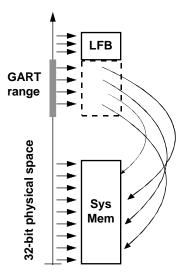

Figure 2-1: Graphics Address Remapping Function

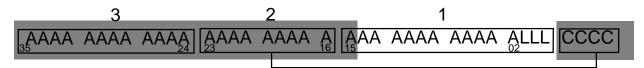

This address remapping applies only to a single, programmable range of the system physical address space, as shown in Figure 2-1. The 32-bit physical address space shown is common to all system agents. Addresses falling in this range are remapped to non-contiguous pages of physical system memory. All addresses not in this range are passed through without modification, and map directly to main system memory, or to device specific ranges, such as the graphics local frame buffer memory shown here.

Remapping is accomplished via a memory-based<sup>1</sup> table called the Graphics Address Remapping Table (GART) and used ("walked") by the corelogic to perform the remapping. In order to avoid compatibility issues and allow future implementation flexibility, this mechanism is specified at a software (API) level. In other words, the actual GART table format is not specified; rather it is abstracted to the API by a HAL or miniport driver that must be provided with the corelogic. While this API does not constrain the future partitioning of remapping hardware, the remapping function will initially be implemented in the chipset or corelogic. *Note: this remapping function should not be confused in any way with the system address translation table mechanism. While some of the concepts are similar, these are completely separate mechanisms which operate independently, under control of the operating system.*

## 2.2 Queuing Models

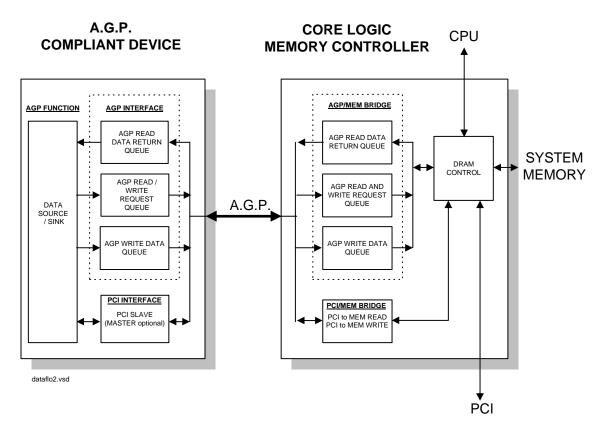

Both A.G.P. bus transactions and PCI bus transactions may be run over the A.G.P. interface. An A.G.P. master (graphics) device may transfer data to system memory using either A.G.P. transactions or PCI transactions. The corelogic can access the A.G.P. master device only with PCI transactions. Traffic on the A.G.P. interface may consist of a mixture of interleaved A.G.P. and PCI transactions. The access request and data queue structures are illustrated in Figure 2-2.

<sup>&</sup>lt;sup>1</sup> The physical location of the table is chipset specific and may reside in main memory or in GART specific memory.

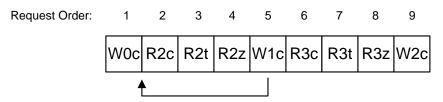

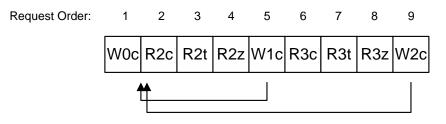

Figure 2-2: A.G.P. Access Queuing Model

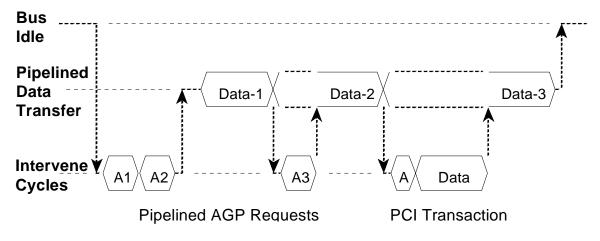

A.G.P. transactions are run in a split transaction fashion where the request for data transfer is "disconnected" from the data transfer itself. The A.G.P. master initiates an A.G.P. transaction with an access request. The corelogic responds to the access request by directing the corresponding data transfer at a later time. The fact that the access requests are separated from the data transfers allows the A.G.P. master to issue several access requests in a pipelined fashion while waiting for the data transfers to occur. Pipelining access requests results in having several read and/or write requests outstanding in the corelogic's *request queue* at any point in time. The request queue is divided into high priority and low priority sub-queues, each of which deal with respective accesses according to separate priority and ordering rules. The A.G.P. master tracks the state of the request queue in order to limit the number of outstanding requests and identify data transactions.

The corelogic processes the access requests present in its request queue. Read data will be obtained from system memory and returned at the corelogic's initiative via the *read data return queue*. Write data will be provided by the A.G.P. device at the corelogic's direction when space is available in the corelogic's *write data queue*. Therefore, A.G.P. transaction traffic will generally consist of interleaved access requests and data transfers.

All PCI transactions on the A.G.P. have their own queues, separate from the A.G.P. transaction queues. Each queue has its own access and ordering rules. Not shown in Figure 2-2 is the corelogic queue which handles processor accesses directly to the PCI target interface of the A.G.P. master, all of which are executed as non-pipelined PCI bus transactions.

### 2.3 Performance Considerations

Deep pipelining capability allows the A.G.P. to achieve a total memory READ throughput equal to that which is possible for memory WRITE<sup>2</sup> transactions. This capability, coupled with optional higher transfer rates and address de-multiplexing, allows a full order of magnitude increase in memory read throughput over today's PCI implementations. However, many typical desktop platforms will not have sufficient total memory performance to allow full utilization of the A.G.P. capabilities, and ultimately platform issues are likely to predominate in the upper performance limit deliverable through the A.G.P. This makes it very difficult to provide as part of this interface specification a single set of performance guarantees or targets the graphics designers can depend upon. It is clear that in order to optimize a graphics design for the most effective use of the A.G.P., it will need to be targeted at a specific subset of platforms and/or corelogic devices.

In an attempt to provide the best possible information for such an optimization, this interface specification defines a few common performance parameters that may be of general interest, and recommends that corelogic vendors and/or OEMs provide these parameters for their systems to respective graphics IHVs.

The following are the basic parameters that each corelogic set and/or system implementation should provide as a performance baseline for IHVs targeting that platform:

- **Guaranteed Latency**: a useable worst case A.G.P. memory access latency via the high priority queue, as measured from the clock on which the request (**REQ#**) signal is asserted until the first clock of data transfer. Assumptions: no outstanding A.G.P. Requests (pipeline empty) and no waitstates or control flow asserted by the graphics master master is ready to transfer data on any clock (inserting *n* clocks of control flow may delay response by more than *n* clocks).

- **Typical Latency**: the typical A.G.P. memory access latency via the low priority queue, as measured from the clock on which the request (**REQ#**) signal is asserted until the first clock of data transfer. Assumptions: no outstanding A.G.P. Requests (pipeline empty) and no waitstates or control flow asserted by the graphics master master is ready to transfer data on any clock (inserting *n* clocks of control flow may delay response by more than *n* clocks).

- Mean bandwidth: deliverable A.G.P. memory bandwidth via the low priority queue, averaged across ~10 ms (one frame display time).

Assumptions: no accesses to the high priority queue; graphics master maintains optimal pipeline depth of <u>x</u>; average access length of <u>y</u>; no waitstates or control flow asserted by the graphics master.

<sup>&</sup>lt;sup>2</sup> Memory read throughput on PCI is about half of memory write throughput, since memory read access time is visible as wait states on this unpipelined bus.

### 2.4 Platform Dependencies

Due to the close coupling of the A.G.P. and main memory subsystem, there are several behaviors of the A.G.P. that will likely end up being platform dependent. While the objective of any specification is to minimize such differences, it is apparent that several are probable among A.G.P. corelogic and platform implementations. This should not, however, have as much impact as it would in other buses for two reasons:

- The A.G.P. is a point-to-point<sup>3</sup> connection, intended for use by a 3D graphics accelerator only, and,

- Due to performance issues (Section 2.3), an A.G.P. graphics master will likely need to be optimized to a specific subset of platform or corelogic implementations anyway.

The purpose of this section is to identify by example some of the areas where behavioral differences are likely, and accordingly establish the scope of this interface specification.

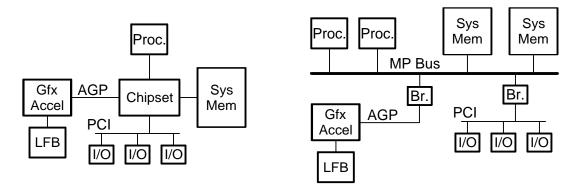

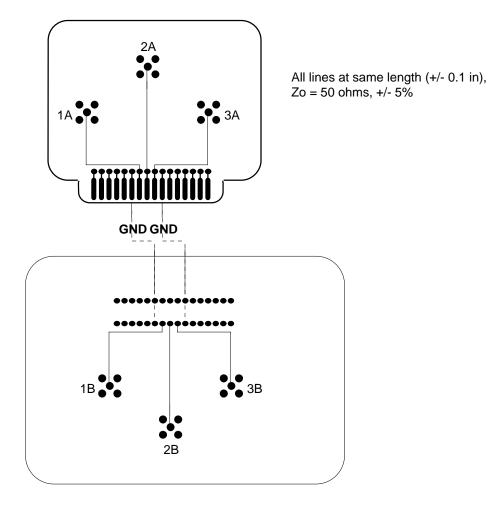

As one example of potential variation, consider the two corelogic architectures shown in Figure 2-3. An integrated approach, typical of desktop and volume systems, is shown on the left, and a symmetric multiprocessor partitioning, typical of MP servers, is shown on the right.

Figure 2-3: Different Corelogic Architectures

The following items are examples of areas where behavioral differences between these or other implementations could well occur:

#### **GART Implementation**

For various reasons, different systems may opt for different GART table implementations and layouts. This, however, is not visible since the actual table implementation is abstracted to a common API by the HAL or miniport driver supplied with the corelogic.

#### **Coherency with Processor Cache**

Due to the high potential access rate on the A.G.P., it is not advisable from a performance perspective to snoop all accesses. Selective snooping in an integrated corelogic architecture presents serious queue

<sup>&</sup>lt;sup>3</sup> This means that active communication can only occur between two A.G.P. agents that reside on the interface, where one agent is referred to as the A.G.P. target and the other the A.G.P. master. The simplest implementation is to only have two devices attached to the bus. Attaching more than two devices to the interface is not precluded as long as there is only one active master and one active target. Any other device must not respond to or interfere with the interface operation. When more than two devices are attached to the interface, the system designer is responsible to ensure that all requirements of this interface specification are met, since the component and/or add-in card designer has no control how the devices are used.

management problems, while the MP bus in an MP corelogic architecture could well deal with selective snoops very easily. As a result, processor cache snooping on A.G.P. accesses is chipset dependent, and may not be counted upon in general. The exact coherency requirements for this interface specification are as follows:

- Processor cache coherency must be guaranteed by the corelogic for all PCI transactions (transactions initiated with the **FRAME#** signal) regardless of which bus segment (A.G.P. or PCI) they originate on. This is consistent with normal PCI operation. Coherency means that at the moment a PCI/A.G.P. memory request is serviced (completed), the subject data are fully consistent with any valid contents of the processor caching mechanism (excluding processor write combining buffers) for any of the target locations in the access.

- For A.G.P. transactions (transactions initiated with the **PIPE#** signal or on the de-multiplexed address bus, **SBA** port), there are no specific coherency requirements, and behavior is chipset dependent. It is entirely possible that some implementations will return stale read data, or allow write data to be overwritten, e.g., by a processor cache write back. Other implementations may provide full coherency support. For this reason, **any device driver managing an A.G.P. device is required to insure that A.G.P. transactions targeted at cacheable memory are safe**. In practice, this caution applies mostly to A.G.P. transactions **outside** the GART address range, since memory allocated **inside** the GART address range by the normal A.G.P. memory allocation procedure will be of a cache type (e.g., WC) consistent with the hardware's native ability to provide coherent access. In general, an A.G.P. device driver may determine the level of chipset coherency support via the chipset ID available in the Microsoft\* Windows\* 95/Windows NT\* registry.

Note: Options for supporting A.G.P. coherent access to cacheable memory (i.e., snooping required) are under consideration. Specific requirements on this topic are subject to change/elaboration.

#### **Bus-to-Bus Traffic Capability**

Bus masters on either the A.G.P. or the PCI bus will routinely access system memory. However, it is possible to also address (PCI) targets on the other bus or port, which effectively requires a PCI-to-PCI bridge in the integrated chipset. Pushing WRITES through this bridge is fairly simple, whereas pushing READS through requires a complete bridge implementation, and it is not clear this would ever be utilized. Therefore, this interface specification only requires support for memory WRITES between a PCI master on the PCI bus and a (PCI) target on the A.G.P.<sup>4</sup> bus. Support of any other transaction between the two interfaces is optional and in general, should not be assumed to work.

#### Address Re-Mapping Support for PCI Bus Master Accesses to Memory

GART range address remapping support is provided by the chipset for graphics devices attached to the A.G.P. interface. Remapping support is, in general, **not** provided for devices attached to standard PCI bus(es). However, to provide a consistent addressing model across the system, this interface specification *requires* the following processor dependent<sup>5</sup>, address remapping support for accesses presented at a PCI port. 1) Chipsets that allow the processor to generate physical addresses in the GART range (i.e., GART address remapping is supported for processor accesses as well as for A.G.P. accesses) *must* support an

<sup>&</sup>lt;sup>4</sup> By way of example, this allows for a video stream generator (e.g., capture, decode, etc.) on PCI to write to the graphics frame buffer on the A.G.P. interface.

<sup>&</sup>lt;sup>5</sup> The chipset implementation of GART remapping is related to the memory management implementation of the attached processor, including, for example, the behavior of MTRRs. However, this reference to processor implementation is made as an example for clarification purposes only. This specification does not place any requirements on processor behavior, nor stipulate any particular processor behavior.

identical remapping service for the PCI port. 2) Chipsets that do not support remapping for processor accesses (i.e., the processor resolves its own GART range addresses to valid physical memory ranges) must NOT do any remapping of addresses presented at the PCI port.

In the case where GART remapping is not provided at the PCI port, any address in the GART address range that is presented at the PCI port must be deemed an access error, and dealt with consistent with the error handling policies of that platform. In general, out of bounds or otherwise erroneous PCI requests do not receive any response and result in a master abort. In *NO* case may an address falling in the GART range be propagated through the corelogic without remapping.

Device drivers managing PCI bus master devices should always use the standard system call to de-reference addresses being passed to the hardware. This will guarantee that the correct address is used for the current platform and level of chipset support. Conversely, device drivers managing A.G.P. bus master devices should always de-reference virtual addresses via the new or alternate system call associated with the new A.G.P. VMM services described in the Memphis DDK. This will guarantee that the linear GART address is always used on the A.G.P. port, independent of platform differences described here. PCI bus master device drivers should *never* use this new de-referencing call.

#### **Monochrome Device Adapter Support**

Existing PCI platforms typically support coexistence of a VGA device with a second monochrome device adapter (MDA), for debug and software development. A.G.P. corelogic implementations may elect to support this capability depending on their specific market needs. Possible implementations include static detection of MDA adapters present off the PCI bus, and rerouting of MDA accesses to the PCI bus under BIOS control; or snooping of A.G.P. directed accesses to dynamically detect disabling of MDA resources on the A.G.P. device and subsequent re-routing to the PCI bus. To ensure interoperation with possible corelogic implementations, additional requirements for A.G.P. graphics controllers with respect to MDA resources are specified in this document (Chapter 6).

#### Performance

As already discussed in Section 2.3, a variety of performance parameters will likely have chipset and/or platform dependencies.

These are examples of platform dependencies that fall outside the scope of this interface specification. In general, the scope of this interface specification is limited to the electrical and logical behavior of the actual A.G.P. interface signals, the mechanical definition of an A.G.P. add-in board, and the A.G.P. configuration registers which control the graphics address remapping function.

# 3. Signals and Protocol Specification

### 3.1 Pin Description

A.G.P. protocol defines 21 new signals beyond what PCI uses. Which of these signals are implemented depends on which features of the bus are supported and whether the device is an A.G.P. master or target. The corelogic is required to support all signals required to:

- 1. Allow the A.G.P. master to enqueue requests and

- 2. Transfer data at 1x or 2x.

The corelogic may optionally support:

- 1. Data transfers at 4x or

- 2. Fast Write (FW) transactions to the A.G.P. master.

The A.G.P. master may optionally choose:

- 1. How it enqueues requests or

- 2. The rate at which it transfers data or

- 3. If it supports FW transactions.

The A.G.P. signals follow the signal type definitions and naming convention used in the *PCI Local Bus Specification*. The following signal type definitions are from the view point of the A.G.P. target:

| in    | <i>Input</i> is an input-only signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| out   | Totem Pole Output is an active driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| t/s   | Tri-State is a bidirectional, tri-state input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| s/t/s | <i>Sustained Tri-State</i> is an active low tri-state signal owned and driven by one<br>and only one agent at a time. The agent that drives an s/t/s pin low must drive<br>it high for at least one clock before letting it float. A new agent cannot start<br>driving an s/t/s signal any sooner than one clock after the previous agent tri-<br>states it. A pull-up is required to sustain the inactive state until another agent<br>drives it, and must be provided by the central resource (A.G.P. target or<br>motherboard). |

The following tables list the signal names in the first column, signal types in the second column, and the signal descriptions in the third column. In the second column, the direction of a t/s or s/t/s signal is from the view point of the corelogic and is represented in the parentheses. For example, **PIPE#** is a sustained tri-state signal (s/t/s) that is always an input for the corelogic. The following tables describe the operation and use of each signal and are organized in four groups: A.G.P. Requests, A.G.P. Flow Control, A.G.P. Status, and A.G.P. Clocking.

| Name      | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIPE#     | s/t/s<br>(in) | <i>Pipelined</i> request is asserted by the current master to indicate a full width request is to be enqueued by the target. The master enqueues one request each rising edge of <b>CLK</b> while <b>PIPE#</b> is asserted. When <b>PIPE#</b> is deasserted, no new requests are enqueued across the <b>AD</b> bus.<br><b>PIPE#</b> is a sustained tri-state signal from a <i>master (graphics controller)</i> and is an input to the <i>target (the corelogic)</i> . |

| SBA[7::0] | in            | <i>SideBand Address port</i> provides an additional bus to pass requests (address and command) to the target from the master. <b>SBA[7::0]</b> are outputs from the master and an input to the target. This port is ignored by the target until enabled (see Section 6.1.10).                                                                                                                                                                                         |

Table 3-1 contains two mechanisms to enqueue requests by the A.G.P. master. The master chooses one mechanism at design time or during the initialization process and is not allowed to change during runtime. When **PIPE#** is used to enqueue requests, the master is not allowed to enqueue requests using the **SBA** port. When the **SBA** port is used to enqueue requests, **PIPE#** cannot be used to enqueue requests.

| Name | Туре | Description                                                                                                                                                                                                                                                                                                                           |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBF# | in   | <i>Read Buffer Full</i> indicates if the master is ready to accept previously requested low priority read data or not. When <b>RBF#</b> is asserted, the arbiter is not allowed to initiate the return of low priority read data to the master. This signal must be pulled up by the central resource (A.G.P. target or motherboard). |

| WBF# | in   | <i>Write Buffer Full</i> indicates if the master is ready to accept FW <sup>6</sup> data from the corelogic or not. When <b>WBF#</b> is asserted, the corelogic arbiter is not allowed to initiate a transaction to provide FW data. This signal must be pulled up by the central resource (A.G.P. target or motherboard).            |

#### Table 3-2: A.G.P. Flow Control

Table 3-2 contains the A.G.P. flow control beyond normal PCI flow control already required. When the master is *always* ready to accept the return of LP (Low Priority) Read data, the A.G.P. master is not required to implement **RBF#** and the corresponding pin on the target is tied (pulled up) in the deasserted state by the central resource. When the master is always ready to accept the first block of FW data, the A.G.P. master is not required to implement **WBF#** and the corresponding pin on the target is tied (pulled up) in the deasserted state by the central resource.

<sup>&</sup>lt;sup>6</sup> Fast Write data is typically data generated by the CPU and *pushed* to the A.G.P. master. See Section 3.5.3.5 for details.

| Name     | Туре | Description                                                                                                                                                                                                                                                                                      |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ST[2::0] | out  | <i>Status</i> bus provides information from the arbiter to the master on what it may do. <b>ST[2::0]</b> only have meaning to the master when its <b>GNT#</b> is asserted. When <b>GNT#</b> is deasserted, these signals have no meaning and must be ignored.                                    |

|          |      | 000 Indicates that previously requested low priority read or flush data is being returned to the master.                                                                                                                                                                                         |

|          |      | 001 Indicates that previously requested high priority read data is being returned to the master.                                                                                                                                                                                                 |

|          |      | 010 Indicates that the master is to provide low priority write data for a previous enqueued write command.                                                                                                                                                                                       |

|          |      | 011 Indicates that the master is to provide high priority write data for a previous enqueued write command.                                                                                                                                                                                      |

|          |      | 100 Reserved (Arbiter must not issue. May be defined in the future by Intel.)                                                                                                                                                                                                                    |

|          |      | 101 Reserved (Arbiter must not issue. May be defined in the future by Intel.)                                                                                                                                                                                                                    |

|          |      | 110 Reserved (Arbiter must not issue. May be defined in the future by Intel.)                                                                                                                                                                                                                    |

|          |      | 111 Indicates that the master has been given permission to start a bus transaction. The master may enqueue A.G.P. Requests by asserting <b>PIPE#</b> or start a PCI transaction by asserting <b>FRAME#</b> . <b>ST[2::0]</b> are always an output from the corelogic and an input to the master. |

| Table 3-3:         A.G.P. Status Signals |

|------------------------------------------|

|------------------------------------------|

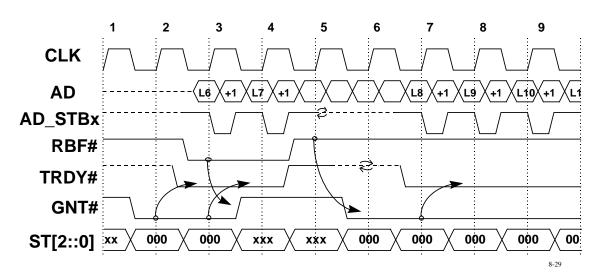

Table 3-3 describes the status signals, which indicate how the **AD** bus will be used for subsequent transactions. The **AD** bus can be used to enqueue new requests, return previously requested read data, or send previously enqueued write data. The **ST[2::0]** signals are qualified by the assertion of **GNT#**.

| Name     | Туре              | Description                                                                                                                                                                                                                                                                 |

|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD_STB0  | s/t/s<br>(in/out) | <b>AD</b> <i>Bus Strobe 0</i> provides timing for 2x data transfer mode on <b>AD[15::00]</b> . The agent that is providing data drives this signal.                                                                                                                         |

| AD_STB0# | s/t/s<br>(in/out) | <b>AD</b> <i>Bus Strobe 0 compliment</i> and <b>AD_STB0</b> provide timing for 4x data transfer mode on <b>AD[15::00]</b> . The agent that is providing data drives this signal.                                                                                            |

| AD_STB1  | s/t/s<br>(in/out) | <b>AD</b> <i>Bus Strobe 1</i> provides timing for 2x data transfer mode on <b>AD[31::16]</b> . The agent that is providing data drives this signal.                                                                                                                         |

| AD_STB1# | s/t/s<br>(in/out) | <b>AD</b> <i>Bus Strobe 1 compliment</i> and <b>AD_STB1</b> provide timing for 4x data transfer mode on <b>AD[31::16]</b> . The agent that is providing data drives this signal.                                                                                            |

| SB_STB   | s/t/s<br>(in)     | <i>SideBand Strobe</i> provides timing for <b>SBA[7::0]</b> (when supported) and is always driven by the A.G.P. master. When the SideBand Strobes have been idle, a synch cycle needs to be performed before a request can be enqueued. (See Section 4.1.2.10 for details). |

| SB_STB#  | s/t/s<br>(in)     | <i>SideBand Strobe compliment</i> and <b>SB_STB#</b> provide timing for <b>SBA[7::0]</b> (when supported) when 4x timing is supported and is always driven by the A.G.P. master.                                                                                            |

| CLK      | t/s<br>(out)      | <i>Clock</i> provides timing for A.G.P. and PCI control signals.                                                                                                                                                                                                            |

| Table 3-4: | A.G.P. | Clock List |

|------------|--------|------------|

|------------|--------|------------|

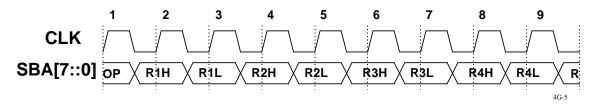

Table 3-4 describes the clock signals used on the A.G.P. interface and when they are used. The basic **CLK** signal is used to time all control signals on the interface and is also used to transfer data in the 1x mode. The other two strobes are used to transfer data on the **AD** bus or the **SBA** port. Since the **AD** bus is 32 bits wide, two copies of the **AD\_STB** are required. When the 4x mode is used, the compliments of the strobes are also required.

#### Table 3-5: USB Signals