# Bringing Communication Networks On Chip: Test and Verification Implications

Bart Vermeulen

John Dielissen

Kees Goossens

Calin Ciordas†

Philips Research Laboratories Prof. Holstlaan 4, 5656 AA Eindhoven The Netherlands † Eindhoven University of Technology {Bart.Vermeulen, John.Dielissen, Kees.Goossens}@philips.com,C.Ciordas@tue.nl

#### Abstract

In this article we present test and verification challenges for system chips that utilise on-chip networks. These systems on a chip (SOCs) and networks on a chip (NOCs) are introduced, where the NOC is exemplified by Philips's ÆTHEREAL NOC architecture. We discuss existing test and verification methods for SOCs and NOCs, and show the particular advantages of using a NOC both for testing and verifying the network, and for testing and verifying the other components of the SOC. This paper is concluded with our experiences with NOCs and a description of on-going work within Philips in this emerging field.

# **1** Introduction

High-performance networking requires dedicated hardware with tremendous computational and communication performance. Network components such as network interfaces and routers are complex systems that are built in a modular fashion by combining many application-specific integrated circuits (ASICs). With increasing packet throughput ASIC performance must increase. Moreover, trends towards differentiated services and higher quality of service require additional performance. Examples are more discerning packet classification, traffic shaping, network management, debug, and so on. To address these issues networking ASICs must become more versatile and programmable, often evolving towards *network processors*.

To indicate that network processors and ASICs are complex systems in themselves, they are usually named *systems on a chip* or SOCs. The number of components in a SOC is growing rapidly, and the communication infrastructure on a single SOC is a major concern. In fact, on-chip interconnect will increasingly be implemented as a *network on a chip* (NOC), complete with network interfaces, routers, and packet or circuit switching. Although the distances over which communication takes place differ by many orders of magnitude, the fields of on-chip networking and computer networking are clearly related.

In Section 2 we show why and how NOCs are used to implement SOC communication needs and we illustrate why their implementation is different compared to computer networks. Section 3 outlines Philips' ÆTHEREAL NOC, which is one such a solution.

In Section 4 we consider how a SOC, constructed from many hardware blocks (called *cores*) and a NOC can be tested for manufacturing defects. Section 5 describes the functional verification of a SOC, the verification of a NOC, and how a NOC can aid in the verification of a SOC. In Section 6 we present how an application, mapped onto a SOC with a NOC, can be verified. We end this paper in Section 7 with conclusions and highlight future work for the development of the Philips ÆTHEREAL NOC.

# 2 Networks on Chip

To manage the complexity of designing a SOC containing multiple cores, design teams are adopting core re-use methodologies. These methodologies allow cores, once they have been designed, to be re-used in multiple SOCs. As a result, the complexity of building a complete SOC shifts from the design of the individual cores to the design of the communication architecture connecting the cores. To prevent the design of this communication architecture from becoming the bottleneck for the design of future SOCs, this communication architecture itself has to be compositional and scalable.

A single broadcast medium, such as Amba and Silicon Backplane [1] buses, can already no longer deliver the required global bandwidth and latency for current SOCs. Switches, such as multi-layer Amba and Prophid, provide some relief, but are ultimately not scalable. Mirroring computer networks, a trend can be observed towards using networks of routers with circuit or packet switching to implement on chip communication [2, 3]. Of particular interest are SOCs for networking applications that themselves use NOCs. Examples of SOCs with an on-chip mesh of packet-switched routers to implement a single-chip switch are given in [4, 5]. Karim et al. [6] show how a network processor for OC-768 uses a hybrid circuit/packet-switched NOC.

Although computer networks and on-chip networks share many requirements, there are also a number of differences, which can lead to different trade offs [2, 7], and hence different architectures. Examples are:

- Quality of service beyond best-effort traffic is probably more important in SOCs for consumer electronics than for Internet services, due to their embedded, real-time, and often safety-critical nature [7]. Consumer applications have to be robust and require predictable performance.

- The conditions on a chip are currently more stable than off chip. On-chip routers are considered either faulty or correct, and hence the network topology is static (and not upgradable) after the chip leaves the factory.

- Routers and network interfaces of a NOC are more resource constrained than those in computer networks because they are intended for main-stream consumer products. As a consequence the chip area must be minimised leading to few and shallow buffers, fast and simple arbitration, limited traffic shaping, etc.

- On-chip communication links are relatively short compared to those in computer networks. Pipelining or transmission-line effects are therefore absent. This advantage partially offsets the severe resource constraints: buffers *can* be small due to the tight synchronisation between routers, and buffer overflow can be prevented by using flow control.

- In contrast to computer networks, inter-router wires are relatively abundant in NOCs [2]. Links can be wide, and their utilisation is probably less important.

Within Philips, the need to manage present-day and future on-chip communication demands spurred the development of the ÆTHEREAL NOC. Details of its architecture are presented in the next section.

# **3** The Æthereal Network on Chip

### 3.1 The Æthereal Architecture

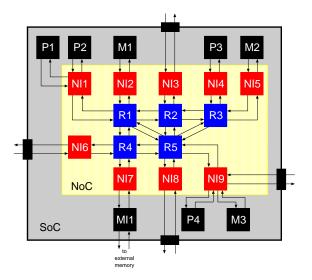

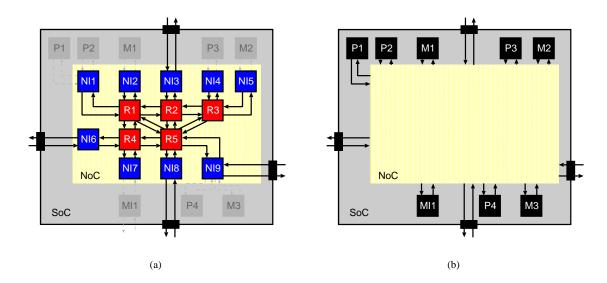

The Philips ÆTHEREAL NOC [7, 8] addresses the communication needs for consumer-electronics SOCs with real-time requirements, as are for example used in digital video set-top boxes. Figure 1 shows an example SOC, consisting of cores and an ÆTHEREAL NOC.

Cores communicate with each other using the NOC, and include memories (Mi), programmable or dedicated processors (Pi), and external memory interfaces (MIi). The NOC consists of routers (Ri) and network

Figure 1: Example SOC with an ÆTHEREAL NOC.

interfaces (NI*i*), which are linked by non-pipelined wires. These routers and NIs are described in more detail in the following subsections.

### 3.2 The Æthereal Router

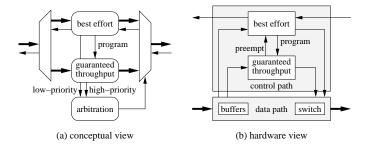

Conceptually, the ÆTHEREAL router module consist of two independent routers, see Figure 2(a).

Figure 2: Two views of the combined GT-BE router.

The *best-effort* (BE) router offers uncorrupted, lossless (flow-controlled), ordered data transport. The *guaranteed-throughput* (GT) router adds hard throughput and latency guarantees over a finite time interval. The GT router fulfils our real-time service requirement, and combining it with a BE router ensures efficient resource utilisation.

#### 3.2.1 The Guaranteed-Throughput Router

To offer not merely statistical, but also hard guaranteed latency the network and hence the routers must be lossless. Besides this easy-to-solve property, also contention must be eliminated or quantified to be able to provide a guarantee. Rate-based and deadline-based scheduling offer guarantees [9], but they require deep output or priority queues. These queues are too costly for on-chip use. A low-cost alternative is to avoid contention completely, by scheduling packets at the network edge such that they are never in the same place, or are never there at the same time, or a combination. The ÆTHEREAL GT router uses a combination of both with time-division-multiplexed pipelined circuits. Every router and network interface block contains

a slot table T(s, o) = i, defining for a given slot *s* from which input *i* output *o* takes its data, if available. For this approach to work, all NOC blocks must share a common notion of time to ensure that their slot tables remain aligned. This is feasible in NOCs by using mesochronous clocking (synchronous clocks with constant skew), or asynchronous hand shaking, as described by Öberg in chapter 8 of [7]. BE packets are used to program the slot tables to set up and tear down GT connections, akin to ATM. This is shown in Figure 2(a) by the arrow labelled "program,". Router programming packets follow the same route as the connection they program. Slot allocations can be computed and programmed at run time in a distributed manner, or can be (pre-)computed off-line and then configured at run time.

#### 3.2.2 The Best-Effort Router

The BE router is a classical input-queued wormhole router, and it uses round-robin arbitration for fairness. Data packets are never reordered in the router, and because deterministic routing is used, ordering is preserved end to end. Programming packets are shunted to a programming module in the router, and spliced in the data stream after they have programmed the slot table.

#### 3.2.3 The Combined Router

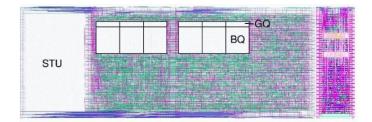

As is shown in Figure 2(b) the control paths of the BE and GT routers are separate, yet interrelated. Moreover, the arbitration unit (including link-level flow control for the BE router) of Figure 2(a) has been merged with the BE router itself. The data path, mainly consisting of the switch matrix, is shared. In computernetwork router architectures the buffers of BE and GT traffic would be stored in a shared RAM. For the small amount of buffering in on-chip routers (in our case, 3 words per GT queue, and 24 words per BE queue) using either RAMs or register-file memories would be very area inefficient. By using dedicated GT and BE hardware fifos (labelled GQ and BQ in Figure 3), the area of the router is reduced by two-thirds.

Figure 3: Lay-out of a combined GT-BE router.

We synthesised an arity 5 router with, a BE queue depth of 24 words of 32 bits, and a 256 slots table (labelled STU) in a 0.12 micron technology. The lay-out is shown in Figure 3. It has an aggregate bandwidth of  $5 \times 500$  MHz  $\times$  32 bit = 80 Gbit/s. The area of the router is 0.26 mm<sup>2</sup> in a 0.12 micron CMOS process using 6 metal layers.

#### **3.3 The Æthereal Network Interface**

The network interface is the bridge between a core and a router, where in general more cores can be connected to one network interface. It implements end-to-end flow control, admission control and traffic shaping, connection set up and tear down, and transaction reordering. Like the router, it contains a slot table, but it has dedicated hardware fifos per connection.

### 4 Manufacturing Test

Like all other SOCs, an NOC-based SOC has to be tested for manufacturing defects. The NOC can be considered as just another core of a SOC, but it is also special in two ways: (1) it is often composed of many identical sub-cores (routers and network interfaces), and (2) it occupies a privileged, central position in the SOC, by virtue of its interconnecting role. In this section we explore the most relevant options for efficiently and effectively testing of a SOC with a NOC.

### 4.1 SOC Manufacturing Test

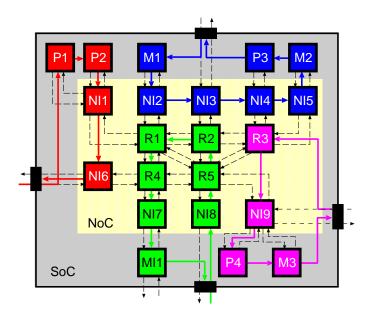

With the design of a scalable and modular SOC comes the issue of testing for manufacturing defects. Over the last years, several advances have been made in SOC testing. IEEE P1500 [10] is standardising a corebased test approach. In this approach, cores are wrapped in a test wrapper to allow easy testing of that core in a SOC. A so-called Test Access Mechanism (TAM) is used in conjunction with test wrappers around the core to transport test data to and from a core-under-test. Combined they allow application-independent test access to all on-chip cores. An example of this core-based test approach is shown in Figure 4.

Figure 4: Default core-based testing

In test mode, the SOC cores are distributed over four TAMs connected to the four I/O interfaces of the chip. In Figure 4, these four TAMs are indicated with the colours red, green, blue, and purple. During scan test all TAMs are used in parallel to minimise the total test time. A disadvantage of this methods is that it requires additional wires to be added to the design to form the TAMs. In network chips, adding these TAMs on top of an already large number of interconnects might cause wire congestion problems during the layout phase of the design.

Built-in Self Test (BIST) is another popular approach to test mainly regular logic blocks, such as for example on-chip memories. Developments have been made to extend the use of BIST to other cores than memories as well. Techniques such as random test pattern generation, in combination with test point insertion or bit-flipping [11] are used to test these blocks efficiently.

As test pattern set one will typically use the traditional stuck-at fault test patterns, complemented by both delay fault test patterns and possibly IDDQ or  $\Delta$ IDDQ test patterns to meet the test quality requirements.

### 4.2 Testing the NOC

Given the NOC's regular and hierarchical structure, it makes sense to adopt a core-based test approach. If we know the function of the core-under-test, i.e. a NOC we can utilise this knowledge to modify the standard core-based test approach to obtain a better-suited test. Figure 5(a) shows a possible core-based approach for an SOC with an NOC.

The blocks that make up the NOC are tested first. If the NOC contains a fault, the entire SOC can be sent off for diagnosis, without testing it further in the production line. This leads to a reduction in test time, and consequently a savings in test cost.

The concept of test re-use can be taken one step further. While testing the NOC, all identical blocks (e.g. all routers) can reuse the same test data. This test data set is broadcast and applied to all routers at the same time. The responses can be compared against each other and any mismatches sent off-chip. This allows for a very efficient pass-fail decision on the NOC. Note that each block still needs to be made uniquely accessible for diagnostic purposes.

Timing tests are also very important for testing a NOC because: (1) all clock boundaries between cores are inside the network interface, and (2) the NOC is spread over the entire SOC and has therefore many long wires. These interconnection wires are more vulnerable to timing errors and cross-talk than others. Sending delay fault test patterns with a high fault coverage over all communication links therefore increases the overall fault coverage. When NOCs become very large, additional test strategies such as those applied in FPGAs can also be included, as for example described by Ubar et al. in chapter 7 of [7].

### 4.3 Testing a SOC through its NOC

After the NOC has been structurally tested, the network can be used to functionally transport test data to and from the cores in a very flexible way. Figure 5(b) shows how the functionality of the NOC is used during the test of the other blocks in the SOC. The NOC is now considered a known-correct block that can be used to transport data from the device pins to the core-under-test and back. An advantage of the re-use of the NOC functionality is that no new TAM wires need to be added to the design, as the existing NOC wires are re-used. The flexibility of the NOC also enables the simultaneous distribution of test data to multiple identical cores. The test data itself can come from off chip, or from an internal BIST module.

When a SOC has structural errors, there are three possibilities: (1) the SOC is thrown away, (2) redundant hardware present on the SOC can replace the faulty cores (repair), or (3) the SOC is sold as a lower-performance SOC. In cases (2) and (3), the NOC's flexibility is used to an advantage. During the manufacturing test, the error information has to be collected and subsequently permanently stored inside the SOC.

# 5 Silicon Verification

Silicon verification involves checking whether the *hardware design* is correct, assuming it has been manufactured correctly. This process is often referred to as silicon debug, as the goal is to try to find any remaining design errors that might have slipped through the pre-silicon verification stages. In this section, we first discuss silicon debug of SOCs and of communication networks. We then look in more detail at the options for verifying a NOC as part of a SOC, and how a NOC can be used for the verification of the other cores of the SOC.

Figure 5: Testing an SOC with a NOC

### 5.1 SOC Silicon Verification

Many companies have adopted design-for-debug strategies to allow prototype silicon to be efficiently and effectively verified [12, 13, 14]. The methods they use can be split into two complementary categories: those that change the configuration of the hardware of the chip to access debug data (intrusive) and those that can acquire debug data in parallel to the functional hardware (non-intrusive).

#### • Intrusive debug

This category covers all debug methods that impact the application before debug data can be examined. These methods add on-chip breakpoint modules to the design of the SOC. These breakpoint modules interrupt the execution of the chip, after an internal sequence of events has been detected. All functional processing is at that point frozen. Various methods are then applied to access internal data. Commonly used access paths included system bus read and writes, TAP-based DMA access, and TAP-based scan-chain access [14].

#### • Non-intrusive debug

This category covers those debug methods that allow examination of debug data in real-time by streaming data for debug to an on-chip memory or out of the chip via a set of dedicated chip pins. Examples include the EJTAG and the IEEE-ISTO 5001 NEXUS standard. These methods add hardware to the design that only observes the functionality of the chip, operating completely in parallel to it. This allows the application to run at the actual operating frequencies. As this debug architecture is completely separated (apart from probe points) for the functional hardware, care must be taken to keep the associated area cost within acceptable limits.

A hybrid solution is often chosen, combining these two methods, depending on the specific debug requirements.

### 5.2 Network Verification

In contrast to the previous section, network verification is about in-field testing. In the prior work on network verification two major areas can be recognized. First of all, a lot of work has been done on network errors: malfunctioning routers, routers that drop out of the network, links that are broken, error detection, etc., and recovery procedures for all these cases. We assume the on-chip ÆTHEREAL network to be very stable, and therefore network errors are not considered further.

The second major area of network verification focuses on bandwidth bottleneck detection and latency monitoring. This can be done either actively or passively. Active monitoring methods involve probing the network with test packets, in order to get round trip latency, peak bandwidth or available bandwidth. The problem with these methods is that they can introduce significant amounts of additional traffic in the network. On the internet, this intrusiveness of the debug traffic can be easily reduced by temporarily increasing the bandwidth with, for example, additional routers. Since this solution cannot be applied on a SOC, the intrusiveness cannot be easily removed, and hence complicates SOC debug.

Passive measurement methods execute performance measurements using special probe devices or probes added to routers, switches or hosts. The measured data is cached. This cached data can be either streamed to a central entity or shared within a local domain. How to best apply the lessons learned in computer networks to the ÆTHEREAL NOCS is an on-going research activity within Philips.

### 5.3 Verifying the NoC

In addition to using the standard verification techniques, an ÆTHEREAL NOC is verifying using special events that have been defined inside the network blocks. With these events, conditions such as incorrect configuration, incorrect topology (e.g. two ports of the router are switched), incorrect initialization, and reset errors can be detected and used to verify applications.

Examples of events in the NI block are: connection opened/closed, data for a connection received, data sent on a connection, and a certain data value appeared on a connection. Examples of events in the router block are: data with a certain path is passing, data in a queue for more than n cycles, incorrect path, and conflicts in reservation. These events can be sent either actively (self-initiating) or passively (polling) Within ÆTHEREAL, the approach is taken to temporary log events on-chip with a local time-stamp, and later, stream them off chip for analysis. Special debugger software uses the event information to graphically represents the state of the network at different levels of detail. This provides the user of the debugger software with very useful debug data. Furthermore the Codebook approach [15] is applied to the off-chip data to correlate the generated events and isolate the root cause of a particular problem.

When deciding to use the on-chip network for transport the events, a choice has to be made to make the implementation either completely independent of the NOC, or to over-dimension the existing network. Note that the latter approach leads to intrusiveness.

### 5.4 Verifying a SOC through its NOC

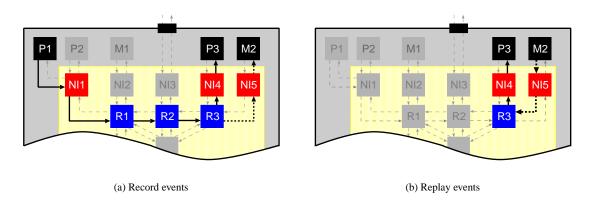

Verification of the SOC contains two parts: verification of the NOC, which is described in the previous section, and verification of the cores. In general the access to the cores is a problem. However, when using a NOC this access is simplified. In Figure 6 one of the possibilities is shown.

A processing block P3 receives data from another processing block P1 via the NOC. If in the verification of P3 a situation has to be reproduced, it is necessary to also repeat P1 and its predecessors. If data from P1 to P3 is first tapped off and streamed to memory M2, P1 needs not be executed during the repetition of P3 in following iterations. When upon replay P3 repeats its fault, the data can easily be streamed off chip and compared with the behavior of for example a FPGA model or or a simulation model. Note that the exact timing of the data is lost during replay. This might lead to the disappearance of the problem, or the introduction of a new problem. Nevertheless, the disappearance of the problem hints at a timing-related problem, which also aids in debugging the application. When the timing, captured at P3, is enforced via specific reservations in the NOC, it is even possible to eliminate this time-intrusiveness. Experiments with varying timing behaviour of the input data can also help to locate the problem.

Beside transporting functional data to a core via the NOC, it is also possible to transport other data. By recording the entire state of a core in an embedded memory, it is possible to quickly restore this state via the NOC prior to replay.

Figure 6: Recording a stream for easy replay in the receiving processing unit.

In this section we have shown that the NOC introduced new options for locating a problem during the verification of the cores. This type of verification is done only once per SOC design. In contrast, verification of an application that is mapped onto a SOC has to be conducted more often, and this is the topic of the next section.

# 6 Application Verification

Although the basic functionality of the SOC is verified using techniques from the previous sections, this by no means implies that the hardware and application software together will also run correctly. Examples of problems that we might detect only after we have mapped an application onto the SOC are:

- a processing core that writes into another core's memory space and thereby corrupts its operation,

- an incompatible format is used to exchange data between cores (e.g. endianess), and

- deadlines are not met because constraints were not passed to the network.

These bugs will become more difficult to find due to the increasing complexity of the SOC itself. Many cores run in parallel and the status of the system can no longer be related to a single program counter, or to traffic on a single bus. It is even possible that some of the cores are executing multi-threaded software and that these cores continue with those processes that can still consume or produce data. Lack of bandwidth, for example due to network congestion or functional processing spread, can cause an application to execute the processes in a different order. Some of the observed problems can be caused by the use of the NOC. However, there are also new opportunities for verifying the complete application using the NOC e.g., breakpoints, spying functional signals, and performance analysis.

- *Breakpoints* in the network can help to analyse the state of the SOC in more detail, as breakpoints can stop (part of) the application by either gating (some of) the on-chip clocks or by putting (part of) the cores in an idle mode. Once (part of) the application is stopped, the on-chip communication architecture can be used to access important registers and memories. Although in principle the *Æ*THEREALS NOC has a global notion of time and can therefore be stopped in relation to this global clock, this is by no means trivial for NOCs in general. Furthermore stopping a SOC is even more complex than stopping a NOC, as all cores can run at their own frequency. This is a topic of on-going research within Philips.

- *Spying functional data* in a local area network can be done relatively easy by plugging a network analyser on that link. This network analyser will monitor all data and process it into required debug or performance information. In a NOC, it is not possible to plug in a similar network analyser because

the data wires of the link are extremely difficult to probe. The two most important aspects we are interested in regarding a link are (1) the possible congestion on the link, and (2) the data from one of the connections that traverses the link. To achieve the first aspect, it is possible to add congestion monitors to the hardware design that can generate breakpoint events. To solve the second aspect, the NI can be configured such that the data is duplicated and sent along a separate debug channel. To reduce the tremendous amount of data that is generated during this functional spying, watchpoints can be introduced. Such a watch-point only gives an indication if a certain value has passed and should be generated inside the NI because, in general, the routers have no knowledge about the data.

• *Performance analysis* data and communication statistics, such as link utilisation, latency, and jitter, are important when debugging an application. One way to gather statistics on latency is to let both the sending and receiving NI blocks generate a event. From the sending NI, the moment at which the data is written in its queue is valuable data. At the receiving NI, this is either the time it arrives, or the time the core retrieves it. The person debugging the application should decide which one is most useful. This is a technique that is also very common in the verification of networks, as was described in Section 5.2

The latter two debug techniques lead to real-time generated data, which can be viewed as network events. These events are an addition to the network events defined in section 5.3, and they can be handled similarly.

# 7 Conclusions and future work

Today and in the future, SOCs will be used to implement high-performance networking applications. One of the issues to be addressed for these SOCs is their on-chip data communication. In this paper we presented the Philips ÆTHEREAL NOC for future-generation SOCs.

With the integration of a network on a SOC come additional test and verification requirements. Fortunately we can still use the wealth of test and verification methods that have already been successfully used in the past for either other existing SOCs and the much-larger communication networks, such as LANs or the Internet. The integrated network also provides new, and complementary possibilities to test and verify the SOC, and with it the SOC application. As shown in this paper, there are plenty of options for meeting a particular SOC's test and verification requirements.

In the initial phase of the ÆTHEREAL project, key elements of future investigation were defined, which include the challenge of stopping a SOC when cores run on their own frequency. Due to dynamic run-time effects (voltage drops, cross-talk, alpha particles, etc.), and their growing size NOCs evolve to computer networks. How to apply the verification lessons learned in computer networks to NOCs in a cost-effective way is another interesting (research) challenge that is currently under investigation within Philips.

In the future, a NOC will most likely become a similar commodity as its bigger brother the Internet, and no doubt equally successful.

# Acknowledgements

The authors like to thank their colleagues Harald Vranken and Jos Huisken and the anonymous reviewers for their valuable feedback on an early draft of this article.

# References

- [1] Drew Wingard. MicroNetworks-based integration for SOCs. In Design Automation Conference, 2001.

- [2] William J. Dally and Brian Towles. Route packets, not wires: On-chip interconnection networks. In *Design Automation Conference*, pages 684–689, June 2001.

#### Bringing Communication Networks On Chip: Test and Verification Implications

- [3] Luca Benini and Giovanni De Micheli. Networks on chips: A new SoC paradigm. IEEE Computer, 35(1):70-80, 2002.

- [4] David Whelihan and Herman Schmit. Memory optimization in single chip network switch fabrics. In *Design Automation Conference*, June 2002.

- [5] HyperChip Inc. Cell-based switch fabric architecture. World International Property Organization Patent number WO 02/098066 A2, December 2002.

- [6] Faraydon Karim, Anh Nguyen, Sujit Dey, and Ramesh Rao. On-chip communication architecture for OC-768 network processors. In *Design Automation Conference*, June 2001.

- [7] Axel Jantsch and Hannu Tenhunen, editors. Networks on Chip. Kluwer, 2003.

- [8] E. Rijpkema, K. G. W. Goossens, A. Rădulescu, J. Dielissen, J. van Meerbergen, P. Wielage, and E. Waterlander. Trade offs in the design of a router with both guaranteed and best-effort services for networks on chip. In *Proceedings of Design Automation* and Test Conference in Europe, March 2003.

- [9] Hui Zhang. Service disciplines for guaranteed performance service in packet-switching networks. *Proceedings of the IEEE*, 83(10):1374–96, October 1995.

- [10] IEEE P1500 Web Site. http://grouper.ieee.org/groups/1500/.

- [11] H. Vranken, F. Meister, and H.-J. Wunderlich. Combining deterministic logic bist with test point insertion. In Proceedings European Test Workshop, pages 105–110, May 2002.

- [12] Don Douglas Josephson, Steve Poehlmann, and Vincent Govan. Debug Methodology for the McKinley Processor. In Proceedings IEEE International Test Conference (ITC), pages 451–460, Baltimore, MD, October 2001.

- [13] H. Hao and R. Avra. Structured design-for-debug the SuperSPARC-II methodology and implementation. In Proceedings IEEE International Test Conference (ITC), pages 175–183, Washington, D.C., October 1995.

- [14] Bart Vermeulen, Tom Waayers, and Sandeep Goel. Core-based Scan Architecture for Silicon Debug. In Proceedings IEEE International Test Conference (ITC), pages 638–647, Baltimore, MD, October 2002.

- [15] S. A. Yemini, S. Kliger, E. Mozes, Y Yemini, and D. Ohsie. High speed and robust event correlation. *IEEE Communications Magazine*, pages 82–90, May 1996.