# Sun Performance Tuning Overview

$A structured approach to improving application performance \ based \\ upon insight into the intricacies of SPARC \ and \ Solaris.$

Sun Microsystems, Inc. 2550 Garcia Avenue Mountain View, CA 94043 U.S.A.

Revision -05, December 1992

© 1992 Sun Microsystems, Inc.—Printed in the United States of America. 2550 Garcia Avenue, Mountain View, California 94043-1100 U.S.A

RESTRICTED RIGHTS LEGEND: Use, duplication, or disclosure by the government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 and FAR 52.227-19.

The products described in this paper may be protected by one or more U.S. patents, foreign patents, or pending applications.

#### **TRADEMARKS**

Sun, Sun Microsystems, the Sun logo, are trademarks or registered trademarks of Sun Microsystems, Inc. UNIX and OPEN LOOK are registered trademarks of UNIX System Laboratories, Inc. All other product names mentioned herein are the trademarks of their respective owners.

All SPARC trademarks, including the SCD Compliant Logo, are trademarks or registered trademarks of SPARC International, Inc. SPARCstation, SPARCserver, SPARCengine, SPARCworks, and SPARCompiler are licensed exclusively to Sun Microsystems, Inc. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK® and  $Sun^{TM}$  Graphical User Interfaces were developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

X Window System is a trademark and product of the Massachusetts Institute of Technology.

# **Contents**

| Prefa | ace                                              | ix |

|-------|--------------------------------------------------|----|

| 1.    | Structure                                        | 11 |

| 2.    | Sourcecode                                       | 13 |

|       | Algorithms                                       | 13 |

|       | Programming Model                                | 15 |

|       | Compiler And Optimisations                       | 17 |

|       | Effective Use Of Provided System Functions       | 18 |

|       | Linking, Localisation Of Reference And Libraries | 19 |

| 3.    | Executable                                       | 21 |

|       | Customising The Execution Environment            | 21 |

|       | The Effects Of Underlying Filesystem Type        | 24 |

| 4.    | Databases & Configurable Systems                 | 27 |

|       | Examples                                         | 27 |

|       | Hire An Expert!                                  | 27 |

|       | Use Sun's Database Excelerator Product           | 27 |

|           | Basic Tuning Ideas                                      | 28         |

|-----------|---------------------------------------------------------|------------|

| <b>5.</b> | Kernel                                                  | 31         |

|           | Buffer Sizes And Tuning Variables                       | 31         |

|           | Paging, MMU Algorithms And PMEGS                        | 35         |

|           | Configuring Out Unused Devices                          | 50         |

|           | References                                              | 50         |

| 6.        | Memory                                                  | <b>5</b> 1 |

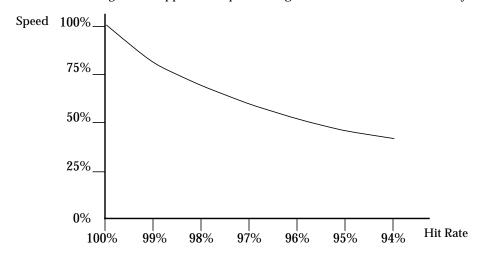

|           | Cache Tutorial                                          | 51         |

|           | Cache line and size effects                             | 52         |

|           | Cache Miss Cost And Hit Rates For Different Machines    | 56         |

|           | I/O Caches                                              | 61         |

|           | Kernel Block Copy                                       | 62         |

| 7.        | Windows and Graphics                                    | 65         |

| 8.        | Disk                                                    | 67         |

|           | The Disk Tuning Performed For SunOS 4.1.1               | 67         |

|           | Throughput Of Various Common Disks                      | 67         |

|           | Sequential Versus Random Access                         | 71         |

|           | Effect Of Disk Controller, SCSI, SMD, IPI               | 71         |

|           | Load Monitoring And Balancing                           | <b>7</b> 4 |

|           | Multiple Disks On One Controller                        | 75         |

|           | Mirrored Disks                                          | 75         |

| 9.        | CPU                                                     | 79         |

|           | Architecture and Implementation                         | 79         |

|           | The Effect Of Register Windows And Different SPARC CPUs | 80         |

|     | Comparing Instruction Cycle Times On Different SPARC CPUs     | 82  |

|-----|---------------------------------------------------------------|-----|

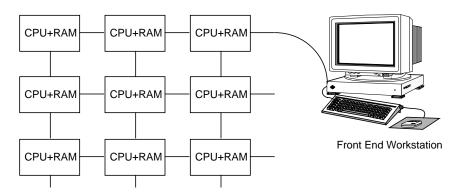

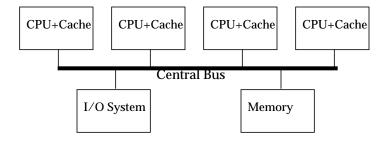

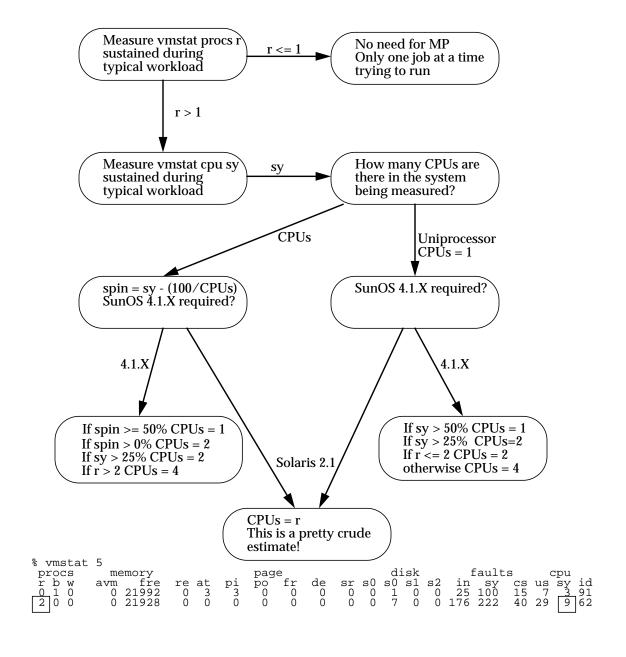

| 10. | Multiprocessors                                               | 89  |

|     | Basic Multiprocessor Theory                                   | 89  |

|     | Unix On Shared Memory Multiprocessors                         | 92  |

|     | SPARC Based Multiprocessor Hardware                           | 94  |

|     | Measuring And Tuning A Multiprocessor                         | 98  |

|     | Programming A Multiprocessor                                  | 100 |

|     | Deciding How Many CPU's To Configure                          | 101 |

| 11. | Network                                                       | 103 |

|     | The network throughput tuning performed for SunOS 4.1 $\dots$ | 103 |

|     | Different ethernet interfaces and how they compare            | 103 |

|     | Using NFS effectively                                         | 105 |

| Α   | References                                                    | 107 |

Contents

# **Tables**

| Table 1  | System Broken Down Into Tuning Layers                                  | 11 |

|----------|------------------------------------------------------------------------|----|

| Table 2  | Resource Limits                                                        | 21 |

| Table 3  | Trace Output with Comments                                             | 22 |

| Table 4  | Tuning SunOS Releases                                                  | 31 |

| Table 5  | Default Settings for Kernel Parameters                                 | 32 |

| Table 6  | Vmstat fields explained                                                | 36 |

| Table 7  | Sun-4 MMU Characteristics                                              | 37 |

| Table 8  | SPARC Reference MMU Characteristics                                    | 40 |

| Table 9  | Application speed changes as hit rate varies with a 25 cycle miss cost | 53 |

| Table 10 | Virtual Write Through Cache Details                                    | 57 |

| Table 11 | Virtual Write Back Cache Details                                       | 57 |

| Table 12 | Physical Write Back Cache Details                                      | 58 |

| Table 13 | On-Chip Cache Details                                                  | 60 |

| Table 14 | Disk Specifications                                                    | 69 |

| Table 15 | 1.3Gb IPI ZBR Disk Zone Map                                            | 70 |

| Table 16 | Which SPARC IU and FPU does your system have?                          | 83 |

| Table 17 | Floating point Cycles per Instruction                         | 86   |

|----------|---------------------------------------------------------------|------|

| Table 18 | Number of Register Windows and Integer Cycles per Instruction | n 87 |

| Table 19 | MP Bus Characteristics                                        | 96   |

| Table 20 | Disabling Processors In SunOS 4.1.X                           | 99   |

| Table 21 | Ethernet Routing Performance                                  | 105  |

### Preface

This paper is an extensive rewrite and update of one originally written for and presented at the Sun User '91 conference of the Sun UK User Group at the NEC, Birmingham, UK. Thanks are due to Daf Tregear and Elwyn Davies of Sun UKUG for imposing the deadlines that forced me to finish what I had started.

The content of this paper is basically a brain dump of everything I have learned over the years about performance tuning. It includes a structured approach to the subject, opinions, heuristics and every reference I could find to the subject.

With competitive pressures and the importance of time to market functionality and bugfixes get priority over designed in performance in many cases. This paper is aimed both at developers who want to design for performance and need to understand Sun's better, and also at end users who have an application and want it to run faster.

There are several good texts on system<sup>1</sup> and network<sup>2</sup> tuning aimed at the system administrator of a network of machines or a timesharing system. This paper takes a different approach and is written primarily from an application developers point of view, although there is much common ground.

$<sup>1.\ &</sup>quot;System\ Performance\ Tuning,\ Mike\ Loukides,\ O'Reilly"$

<sup>2. &</sup>quot;Managing NFS and NIS, Hal Stern, O'Reilly"

The information presented in this paper has all been gleaned from published sources and to my knowledge it does not contain any proprietary information. It is intended to be available for reference by Sun users everywhere.

Since the public release of this paper in September 1991 I have had a lot of feedback from readers. Particular thanks for detailed comments and contributions go to Brian Wong, Keith Bierman, Hal Stern and Dave Rosenthal of Sun and Gordon Irlam of Adelaide University.

All errors, opinions and omissions are mine.

Any comments, corrections or contributions should be made to the address below.

Adrian Cockcroft Sun Microsystems Ltd. 306 Science Park Milton Road Cambridge CB5 4WG UK

Internet Email: adrian.cockcroft@uk.sun.com UKnet Email: adrian.cockcroft@sun.co.uk

### Structure

There have been many white papers on performance tuning and related topics for Suns. This one attempts to gather together references, provide an overview, bring some information up to date and plug some gaps. A cookbook approach is taken where possible and I have attempted to stick my neck out and provide firm recommendations based upon my own experience. The rate at which the operating system and underlying hardware change is a major challenge to anyone trying to work with computers so older software and hardware is mentioned where appropriate to show how the base level of tuning has improved with time.

The performance characteristics of a system can be viewed in a layered manner with a number of variables affecting the performance of each layer. The layers that I have identified for the purposes of this paper are listed below together with some example variables for each layer. The chapters of this paper look at each layer in turn and the appendix has details of the references.

Table 1 System Broken Down Into Tuning Layers

| Layers                                  | Variables                                        |  |

|-----------------------------------------|--------------------------------------------------|--|

| Sourcecode                              | Algorithm, Language, Programming model, Compiler |  |

| Executable Environment, Filesystem Type |                                                  |  |

| Database                                | Buffer Sizes, Indexing                           |  |

| Kernel                                  | Buffer Sizes, Paging, Tuning, Configuring        |  |

| Memory                                  | Cache Type, Line Size And Miss Cost              |  |

| Disk                                    | Driver Algorithms, Disk Type, Load Balance       |  |

| Windows & Graphics                      | Window System, Graphics Library, Accelerators    |  |

| CPU                                     | Processor Implementation                         |  |

| Multiprocessors                         | Load Balancing, Concurrency, Bus Throughput      |  |

| Network                                 | Protocol, Hardware, Usage Pattern                |  |

### Sourcecode

This chapter is concerned with variables that the programmers specifying and writing the software can control.

### Algorithms

Many algorithms are invented while writing a program and are as simple to code as possible. More efficient algorithms are often much more complex to implement and may need to be retrofitted to an application that is being tuned. A good book of algorithms<sup>1</sup> and a feel for which parts of the program are likely to be hot spots can make more difference to performance than all other tuning tweaks put together. There are some general classes of algorithms with behaviors as shown below.

### Algorithmic Classification

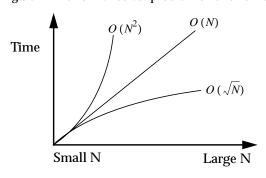

Figure 1 Performance vs. problem size for different classes of algorithms

$<sup>1.\</sup> Algorithms\ by\ Sedge wick\ is\ a\ digestible\ alternative\ to\ Knuth's\ definitive\ reference.$

The notation O(N) means that as the amount of data increases by a factor of N the time taken increases by the same order of magnitude. A higher order increase, for example where the time taken increases by the order of N squared, needs to be avoided. Lower order increases are what the textbook algorithms are trying to achieve.

As long as a program is being used with a small data-set the difference between the different classes of algorithms is minor. This is often the case during testing or in the early lifetime of a product.

### An Example Problem

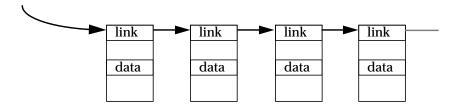

One example could be a CAD system that keeps each object in a drawing on a linked list and performs a linear search through the list whenever it needs to find an object. This works for small drawings and it is not too bad if the time taken to perform other operations dominates the execution time. If the CAD system is ported from a Sun3/60 to a SPARCstation 2 then many parts of the code speed up by a factor of perhaps 10 times. The users now expect to run drawings with 10 times the complexity at the same speed as a Sun3/60.

Unfortunately for some operations the time taken to search through the linked list now dominates and the linked list code doesn't see a 10 times speedup due to caching effects (see "A Problem With Linked Lists" on page 54) so there is a performance problem and the algorithm needs to be improved. The solution in this case is to move from a linear search to a more complex search based on hash tables or tree structures. Another approach is to incrementally sort the linked list so that commonly accessed entries are at the beginning.

### Space Versus Time

Another issue to consider is space versus time optimization. There's no sense in making an algorithm that's  $O(N^2)$  run in O(N) time if doing so requires going from O(N) to  $O(N^2)$  space. The increase in storage will probably make the application page, and the disk accesses outweigh any improvement in CPU run time. It is possible to make an algorithm efficient only to use so much space that it doesn't run at the full CPU speed.

### Programming Model

There is often a conceptual framework underlying an application which can be thought of in terms of a programming model. Some example models are:

- Hierarchical, structured programming via Jackson Diagrams

- Object Oriented

- Dataflow, the Yourdon/DeMarco method

- State Machines

- Numerical Algorithms

- AI based, rules or knowledge based design

- Forms and records

- Entity relations

Sometimes the model that a programmer or system designer prefers is chosen regardless of the type of system being written. An inappropriate match between the programming model and the problem to be solved is a remarkably common cause of performance problems.

### Choice of language to express the algorithm or model

The programmer may decide to choose a language that is familiar to him or may have a language imposed on him. Often the language ends up dictating the programming model, irrespective of the needs of the application, but sometimes languages are forced to implement programming models that are inappropriate. Real examples include a database system written in APL, a real-time control system written in Prolog and a very large message passing object oriented system written in C.

If there is a good match of problem to programming model to language then there is a good chance that the system overall will respond well to tuning. Poorly matched systems sometimes contain so much unnecessary complexity that brute force increases in CPU and I/O throughput are the only thing that has a significant effect.

The moral is that if you come across an application like this and first attempts at tuning have little effect you may as well put your money into buying a faster Sun and your time and effort into redesigning the system from scratch.

It comes down to using the right tool for the job. Most people know what languages to use for particular jobs but some non-obvious points are listed below.

#### Fortran

Fortran is usually the fastest language for anything that is numerically intensive. For an equivalent level of compiler technology it will always be faster than C. This is because it has a simple structure that compilers can handle more easily than C and it doesn't have pointers so there is less chance of side effects during expression evaluation. The key to optimisation is code motion and this can be performed more safely in Fortran than in C. A second reason is that Fortran defaults to passing floating point variables by reference (i.e. passing an address rather than the number itself) which is more efficient, especially on processors, like SPARC, that have separate integer and floating point registers and pass parameters in integer registers.

#### Assembler

In theory assembler is the fastest language possible. In practice programmers get so bogged down in the huge volume of code and the difficulty in debugging it that they tend to implement simple, inefficient algorithms in poorly structured code. It is hard to find out where the hot spots in the system are so the wrong parts of the system get optimised. When you discover a small routine that dominates the execution time, look at the assembler generated by the compiler and tweak the sourcecode. As a last resort consider rewriting it in assembler.

It is often very helpful to understand what sort of code is generated by your compiler. I have found that writing clean simple high level language code can help the compiler to understand the code better and that this can improve the optimisation of the generated assembler. Just think of assembler as read-only code. Read it and understand it but don't try to write it.

#### *C* and *C*++

It seems that just about everything is written in C nowadays. Its biggest weakness is that hardly anyone seems to use lint to check their code as a standard part of their compilation makefiles. Wading through the heaps of complaints that lint produces for most systems written in C gives a pretty good

insight into the sloppy nature of much C coding. Many problems with optimisers breaking C code can be avoided by getting the code to lint cleanly first! ANSI C is an improvement but not a substitute for lint.

C++ should be used whenever an object oriented design is called for. C could be used in most cases but the end result is that sloppy coding and programmers who take shortcuts, combined with the extra level of complexity, make the resulting systems very hard to debug and hence give optimisers a hard time. Writing C++ like code in C makes the code very hard to understand, it is much easier to use a C++ preprocessor, with a debugger and performance analyser that understand the language.

### Debug And Test Tools

Lint has just been mentioned, build it into your default makefiles and use it regularly. There is a little known utility called tcov<sup>1</sup> that performs test coverage analysis and produces an annotated listing showing how many times each block of code has been executed and a percentage coverage figure.

There is a product called Purify<sup>2</sup> that can be used to debug subtle errors in C and C++ programs such as used-before-set data, memory allocation errors and array bounds violations. It works by modifying object files to instrument memory references so it can find errors in library routines and it slows down execution by no more than a factor of three.

### Compiler And Optimisations

Having chosen a language, there is a choice of compilers for the language. There are typically several compilers for each major language on SPARC. The SPARCompilers from SunPro tend to have the largest user base and the best robustness on large programs. The Apogee C and Fortran compilers seem to have a performance advantage of 10-20% over the commonly used SunPro SPARCompilers 1.0 release for programs (like SPEC benchmarks) that can use maximum optimisation but the Apogee compilers are much less robust. The recent SPARCompilers 2.0 release narrows the performance gap and some preliminary results for SPARCompilers 3.0 show very similar results.

<sup>1.</sup> See the tcov manual page.

<sup>2.</sup> Described in a paper presented at Usenix, Winter 92.

Competition between SunPro, Apogee and others will fuel a drive to better compilers. Using compilers effectively to tune code is not covered in this paper since it has been addressed in great depth in previous publications <sup>123</sup>. To summarise in a sentence: clean C code with lint, turn up the optimiser most of the way, profile to find hot spots and turn up the optimiser for those parts only. Look at the code in the hot spots to see if the algorithm is efficient.

### Effective Use Of Provided System Functions

This is a general call to avoid re-inventing the wheel. The SunOS libraries contain many high level functions that have been debugged tuned and documented for you to use. If your system hot-spot turns out to be in a library routine then it may be worth looking at re-coding it in some streamlined way, but the next release of SunOS or the next generation of hardware may obsolete your homegrown version. As an example, the common string handling routines provided in the standard SunOS 4.X C library are simple compiled C code. In Solaris 2 these routines are written in optimised assembler.

There are some very powerful library routines that seem to be under-used.

### Mapped files

SunOS 4.0 and all versions of Unix System V Release 4 (SVR4) include a full implementation of the mmap system call. This allows a process to map a file directly into its address space without the overhead of copying from kernel to user space. It also allows shared files so that more efficient use of memory is possible and inter-process communication can be performed<sup>4</sup>.

### Asynchronous I/O

This is an extension to the normal blocking read and write calls to allow the process to issue non-blocking reads and writes<sup>5</sup>.

$<sup>1. \ \</sup> Numerical\ Computation\ Guide, supplied\ with\ SunC\ and\ SunFortrand$

<sup>2.</sup> You and Your Compiler, by Keith Bierman

$<sup>{\</sup>bf 3.}~SPARCompiler~Optimisation~Technology~Technical~White~Paper~\\$

$<sup>{\</sup>bf 4.\ SunOS\ 4.1\ Performance\ Tuning}$

<sup>5.</sup> aioread, aiowrite manual pages

### Memory Allocation Tuning

The standard version of malloc in the Sun supplied libc is optimised for good space utilisation rather than fast execution time. A version of malloc that optimises for speed rather than space uses the 'BSD malloc' algorithm and is provided in /usr/lib/libbsdmalloc.a.

There are some powerful options in the standard version of malloc<sup>1</sup>.

- mallocmap() prints a map of the heap to the standard output.

- mallopt() configures quick allocation of small blocks of memory.

- mallinfo() provides statistics on malloc.

The small block allocation system controlled by mallopt is not actually implemented in the code of the default version of malloc or the BSD malloc.

### Linking, Localisation Of Reference And Libraries

There are two basic ways to link to a library in SunOS and SVR4, static linking is the traditional method used by other systems and dynamic linking is a runtime link process. With dynamic linking the library exists as a complete unit that is mapped into the address space of every process that uses it. This saves a lot of RAM, particularly with window system libraries at over a megabyte each. It has several implications for performance tuning however.

Each process that uses a shared library shares the physical pages of RAM occupied by the library, but uses a different virtual address mapping. This implies that the library will not be at a fixed point in the address space each time it is used. In fact it can end up in different places from one run of a program to the next and this can cause caching interactions that increase the variance of benchmark results. The library must also be compiled using position independent code which is a little less efficient than normal code and has an indirect table jump to go through for every call that is a little less efficient than a direct call. Static linking is a good thing to use when benchmarking systems but production code should dynamically link, particularly to the system interface library libc. A mixture can be used, for example in the following compilation the fortran library is statically linked but libc is dynamically linked.

1. malloc manual page

% f77 -fast -o fred fred.f -Bstatic -lF77 -lV77 -lm -Bdynamic -lc

This dynamically links in the <code>libc</code> library and makes everything else static. The order of the arguments is important. This is one of those tricks that is hard to work out and not documented anywhere else so make a note of it! If you are shipping products written in Fortran to customers who do not have Fortran installed on their systems you will need to use this trick.

#### Tuning Shared Libraries

When using static linking the library is accessed as an archive of separate object files and only the files needed to resolve references in the code are linked in. This means that the position of each object module in memory is hard to control or predict. For dynamic linking the entire library is provided at run time regardless of which routines are needed. In fact, the library is demand paged into memory as it is needed. Since the object modules making up the library are always laid out in memory the same way a library can be tuned when it is built by reordering it so that modules that call each other often are in the same memory page. In this way the working set of the library can be dramatically reduced. The window system libraries for sunview and OpenWindows are tuned in this way since there is a lot of inter-calling between routines in the library. Tools to do this automatically on entire programs or libraries are provided as part of the SPARCworks 2.0 Analyser using some functionality that is only provided in the Solaris 2 debug interface (/proc), linker and object file format. The main difference is that the a.out format used in BSD Unix and SunOS 4 only allows entire object modules to be reordered. The ELF format used in Unix System V.4 and Solaris 2 allows each function and data item in a single object module to be independently relocated.

20

## Executable

This section is concerned with variables that the user running a program on a Sun can control on a program by program basis.

### Customising The Execution Environment

### Limits

The execution environment is largely controlled by the shell. There is a limit command which can be used to constrain a program that is hogging too many resources. The default SunOS 4.1.X resource limits are shown in Table 2.

Table 2 Resource Limits

| Resource name | Default limit |

|---------------|---------------|

|               | 14 4: 1       |

| cputime       | unlimited     |

| filesize      | unlimited     |

| datasize      | 524280 Kbytes |

| stacksize     | 8192 Kbytes   |

| coredumpsize  | unlimited     |

| memoryuse     | unlimited     |

| descriptors   | 64            |

The most useful changes to the defaults are to prevent core dumps from happening when they aren't wanted:

% limit coredumpsize 0

To run programs that use vast amounts of stack space:

% limit stacksize unlimited

To run programs that want to open more than 64 files at a time:

% limit descriptors 256

### Tracing

When tuning or debugging a program it is often useful to know what system calls are being made and what parameters are being passed. This is done by setting a special bit in the process mask via the trace command. Trace then prints out the information which is reported by the kernel's system call interface routines. Trace can be used for an entire run or it can be attached to a running process at any time. No special compiler options are required. In Solaris 2 trace has been renamed truss.

Here's some trace output with commentary added to sort the wheat from the chaff. It also indicates how cp uses the mmap calls and how the shared libraries start up.

Table 3 Trace Output with Comments

| open ("/usr/lib/ld.so", 0, 04000000021) = 3  ead (3, "", 32) = 32  Get the shad a.ou | on a cp command ared library loader It header to see if dynamically linked de to memory Ta to memory |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| ead (3, "", 32) = 32                                                                 | t header to see if dynamically linked de to memory                                                   |

|                                                                                      | de to memory                                                                                         |

| nmap (0, 40960, 0x5, 0x80000002, 3, 0) = 0xf77e0000 Map in co                        |                                                                                                      |

|                                                                                      | ta to memory                                                                                         |

| nmap (0xf77e8000, 8192, 0x7, 0x80000012, 3, 32768) = 0xf77e8000 Map in dat           |                                                                                                      |

| open ("/dev/zero", 0, 07) = 4 Get a supp                                             | oly of zeroed pages                                                                                  |

| getrlimit (3, 0xf7fff8b0) = 0 Read the li                                            | imit information                                                                                     |

| nmap (0xf7800000, 8192, 0x3, 0x80000012, 4, 0) = 0xf7800000 Map /dev/2               | zero to the bss?                                                                                     |

| close (3) = 0 Close Id.so                                                            | 0                                                                                                    |

| getuid () = 1434 Get user id                                                         | t l                                                                                                  |

| getgid () = 10 Get group                                                             | id                                                                                                   |

| open ("/etc/ld.so.cache", 0, 05000000021) = 3                                        | shared library cache                                                                                 |

| stat (3, 0xf7fff750) = 0 See if cach                                                 | ne is up to date                                                                                     |

| nmap (0, 4096, 0x1, 0x80000001, 3, 0) = 0xf77c0000 Map it in to                      | read it                                                                                              |

| close (3) = 0 Close it                                                               |                                                                                                      |

| ppen ("/usr/openwin/lib", 0, 01010525) = 3 LD_LIBRA                                  | ARY_PATH contains /usr/openwin/lib                                                                   |

| stat $(3, 0xf7fff750) = 0$ so look the                                               | ere first                                                                                            |

| nmap (0xf7802000, 8192, 0x3, 0x80000012, 4, 0) = 0xf7802000                          |                                                                                                      |

| getdents (3, 0xf78000d8, 8192) = 1488 Get some                                       | directory entries looking for the right                                                              |

| yetdents (3, 0xf78000d8, 8192) = 0 version of                                        | the library                                                                                          |

| close (3) = 0 Close /usr                                                             | /openwin/lib                                                                                         |

| open ("/usr/lib/libc.so.1.6", 0, 032724) = 3 Get the sh                              | ared libc                                                                                            |

| ead (3, "", 32) = 32 Check its 0                                                     | OK                                                                                                   |

| nmap (0, 458764, 0x5, 0x80000002, 3, 0) = 0xf7730000 Map in the                      | code                                                                                                 |

Table 3 Trace Output with Comments

| Trace Output                                                        | Comments                  |

|---------------------------------------------------------------------|---------------------------|

| mmap $(0xf779c000, 16384, 0x7, 0x80000012, 3, 442368) = 0xf779c000$ | Map in the data           |

| close (3) = 0                                                       | Close libc                |

| close (4) = 0                                                       | Close /dev/zero           |

| open ("NewDocument", 0, 03) = 3                                     | Finally! open input file  |

| fstat(3, 0xf7fff970) = 0                                            | Stat its size             |

| stat ("Tuning", 0xf7fff930) = -1 ENOENT (No such file or directory) | Try to stat output file   |

| stat ("Tuning", 0xf7fff930) = -1 ENOENT (No such file or directory) | But it's not there        |

| creat ("Tuning", 0644) = 4                                          | Create output file        |

| mmap $(0, 82, 0x1, 0x80000001, 3, 0) = 0xf7710000$                  | Map input file            |

| mctl (0xf7710000, 82, 4, 0x2) = 0                                   | Madvise sequential access |

| write (4, "This is a test file for my paper", 82) = 82              | Write out to new file     |

| munmap $(0xf7710000, 82) = 0$                                       | Unmap input file          |

| close (3) = 0                                                       | Close input file          |

| close (4) = 0                                                       | Close output file         |

| close(0) = 0                                                        | Close stdin               |

| close (1) = 0                                                       | Close stdout              |

| close (2) = 0                                                       | Close stderr              |

| exit (0) = ?                                                        | Exit program              |

| %                                                                   |                           |

### **Timing**

The C shell has a built-in time command that is used when benchmarking or tuning to see how a particular process is running.

```

% time man madvise

...

0.lu 0.5s 0:03 21% 0+168k 0+0io 0pf+0w

%

```

In this case 0.1 seconds of user cpu and 0.5 seconds of system cpu were used in 3 seconds elapsed time which accounted for 21% of the cpu. The growth in size of the process, the amount of i/o performed and the number of page faults and page writes are recorded. Apart from the times, the number of page faults is the most useful figure. In this case everything was already in memory from a previous use of the command.

### The Effects Of Underlying Filesystem Type

Some programs are predominantly I/O intensive or may open and close many temporary files. SunOS has a wide range of filesystem types and the directory used by the program could be placed onto one of the following types.

#### **UFS**

The standard filesystem on disk drives is the Unix File System, which in SunOS 4.1 and on is the Berkeley Fat Fast Filesystem. If your files have more than a temporary existence then this will be fastest. Files that are read will stay in RAM until a RAM shortage reuses the pages for something else. Files that are written get sent out to disk but the file will stay in RAM until the pages are reused for something else. There is no special buffer cache allocation, unlike other Berkeley derived versions of Unix. SunOS and SVR4 both use the whole of memory to cache pages of code, data or I/O and the more RAM there is the better the effective I/O throughput will be. See the disk chapter for more info.

### tmpfs

This is a real RAM disk filesystem type. Files that are written never get put out to disk as long as there is some RAM available to keep them in. If there is a RAM shortage then the pages end up being stored in the swap space. The most common way to use this is to un-comment the line in /etc/rc.local for mount /tmp . Some operations, such as file locking, are not supported in early versions of the tmpfs filesystem so applications that lock files in /tmp will misbehave. This is fixed in SunOS 4.1.2 and tmpfs is the default in Solaris 2.

```

# The following will mount /tmp if set up in /etc/fstab.

# If you want to use

# the anonymous memory based file system,

# have an fstab entry of the form:

swap

/tmp

tmp rw 0 0

# Make sure that option TMPFS is configured in the kernel

# (consult the System and Network Administration Manual).

mount /tmp

One side effect of this is that the free swap space can be seen using df.

% df /tmp

Filesystem

kbytes

used

avail capacity Mounted on

15044

808

14236

5%

swap

/tmp

```

### **NFS**

This is a networked filesystem coming from a disk on a remote machine. It tends to have reasonable read performance but can be poor for writes and is slow for file locking. Some programs that do a lot of locking are unusable on NFS mounted filesystems. See the networking chapter for more information on tuning NFS performance.

### References

• "tmpfs: A Virtual Memory File System, by Peter Snyder"

# Databases & Configurable Systems

This chapter is concerned with tuning programs, such as databases, that the user is relying on in order to run his own application. The main characteristic is that these programs may provide a service to the system being tuned and they have sophisticated control or configuration languages.

### **Examples**

Examples include relational databases such as Oracle, Ingres, Informix and Sybase which have large numbers of configuration parameters and an SQL based configuration language; CAD systems such as Autocad and Medusa; and Geographical Information Systems systems such as Smallworld GIS which have sophisticated configuration and extension languages.

### Hire An Expert!

For serious tuning you either need to read all the manuals cover to cover and attend training courses or hire an expert for the day. The black box mentality of using the system exactly the way it came off the tape with all parameters set to default values will get you going but there is no point tuning the rest of the system if it spends 90% of its time inside a poorly configured database.

### Use Sun's Database Excelerator Product

Sun has a version of SunOS tuned for use on systems with large amounts of memory running databases. It is called DBE - Database Excelerator and there are versions for each recent release of SunOS; DBE 1.2 for SunOS 4.1.2 and DBE 1.3 for SunOS 4.1.3. It is cheap at a few hundred pounds for media, manual and site licence, and it can dramatically improves the performance of databases, particularly with large numbers of concurrent users. If used on a system with less than 16 Mb of RAM it is likely to run more slowly than the standard SunOS since several algorithms have been changed to improve speed at the expense of more memory usage so 16 Mb is the minimum configuration.

### Basic Tuning Ideas

Several times I have discovered untuned copies of Oracle so some basic recommendations on the first things to try may be useful. They apply to other database systems in principle.

### Increasing Buffer Sizes

Oracle uses an area of shared memory to cache data from the database so that all oracle processes can access the cache. It defaults to about 400Kbytes but it can be increased to be bigger than the entire data set if needed. I would increase it to about 10% of the total RAM in the machine as a first try. There are ways of looking at the cache hit rate within Oracle so increase the size until the hit rate stops improving or the rest of the system starts showing signs of memory shortage. Avoiding unnecessary random disk I/O is one of the keys to database tuning.

### Using raw disk rather than filesystems

You should reserve at least three empty disk partitions, spread across as many different disks and controllers as possible (but avoiding the *a* or *c* partition) when installing SunOS. You can then change the raw devices to be owned by oracle and when installing Oracle specify the raw devices rather than files in the usual filesystem as the standard data, log1 and log2 files. Filesystems incur more CPU overhead than raw devices and can be much slower for writes due to inode and indirect block updates. Two or three blocks in widely spaced parts of the disk must be written to maintain the filesystem, while only one block needs to be written on a raw partition. I have anecdotal reports of a doubling in database performance when moving from filesystems to raw partitions.

#### Balance The Load Over All The Disks

The log files should be on a separate disk from the data if possible. This is particularly important for databases that have a lot of update activity. It will also help to put indexes on their own disk or to split the database tables over as many disks as possible. The system disk is often lightly used and on a two disk system I would put the log files on the system disk and put the rest on its own disk. See "Load Monitoring And Balancing" on page 74.

#### Which Disk Partition To Use

If you use the first partition on a disk as a raw oracle partition then you will lose the disk's label. This can be recovered using the format command if you are lucky but you should make a filesystem, swap space or small unused partition at the start of the disk.

On Sun's 424Mb and 1.3Gb disks the first part of the disk is the fastest so a tiny first partition followed by a database partition covering the first half of the disk is recommended for best performance. See "ZBR Drives" on page 70 for more details and an explanation.

#### The Effect Of Indexes

When you look up an item in a database it must match your request against all the entries in a (potentially large) table. Without an index a full table scan must be performed and the database will read the entire table from disk in order to search every entry. If there is an index on the table the database will lookup the request in the index and it will know which entries in the table need to be read from disk. Some well chosen indexes can dramatically reduce the amount of disk I/O and CPU time required to perform a query. Poorly designed or untuned databases are often under-indexed.

### Kernel

This chapter is concerned with variables that can be changed by a system administrator building or tuning a kernel. In SunOS 4.X the kernel must be recompiled after tweaking a parameter file to increase table sizes but in Solaris 2 there is no need to re-compile the kernel, it is modified by changing /etc/system. The kernel algorithms have not changed much between SunOS 4.X and System V.4 or Solaris 2. The differences are noted as SVR4 changes if they are generic and as Solaris 2 where Solaris 2 is different to generic SVR4.

Later releases of SunOS 4.X have Solaris 1.X names which I have avoided for clarity. Part of Solaris 2.0 is known as SunOS 5.0 but this name is little used.

### **Buffer Sizes And Tuning Variables**

The number of fixed size tables in the kernel has been reduced in each release of SunOS. Most are now dynamically sized or are linked to the maxusers calculation. The tuning required for each release varies as shown below.

Table 4 Tuning SunOS Releases

| Release     | Extra Tuning Required (apart from maxusers)           |

|-------------|-------------------------------------------------------|

| SunOS 4.0   | Number of streams, number of mbufs                    |

| SunOS 4.0.1 | Same as SunOS 4.0                                     |

| SunOS 4.0.3 | Add PMEGS patch tape, set handspread                  |

| SunOS 4.1   | Add PMEGS patch tape or DBE-1.0, set handspread       |

| SunOS 4.1.1 | Add DBE-1.1, increase buffer cache                    |

| SunOS 4.1.2 | Add DBE-1.2, add I/O patch 100575-02, increase maxslp |

| SunOS 4.1.3 | Add DBE-1.3, Increase maxslp                          |

| Solaris 2.0 | Increase paging parameters, check /etc/TIMEZONE       |

#### Maxusers In SunOS 4.X

The maxusers parameter is set in the kernel configuration file. Many parameters and kernel tables are derived from it. It is intended to be derived from the number of users on the system but this usually results in too small a value. It defaults to 16 for the sun4m architecture, but for other architectures it defaults to 8 for a GENERIC kernel and 4 for a GENERIC\_SMALL. These values are suitable for single user workstations that are short of RAM but in most cases a substantial increase in maxusers is called for. A safe upper limit is documented in the SunOS 4.1.2 (about 100) and 4.1.3 (225) manuals and a very rough guideline would be to set to the number of Megabytes of RAM in the system for a workstation and twice that for an NFS server. Due to a shortage of kernel memory in SunOS 4.1.2 the safe upper limit is *reduced* to about 100 for systems that have large amounts of RAM since kernel memory is used to keep track of RAM as well as to allocate tables. The kernel base address was changed in 4.1.3 to allow a safe limit of 225 for any system.

#### Maxusers in Solaris 2

The effect of maxusers has not changed but it now defaults to 8 and is modified by placing commands in /etc/system e.g.

set maxusers=32

Be very careful with set commands in /etc/system, they basically cause automatic adb patches of the kernel so there is plenty of opportunity to completely screw up your system. The "Administering Security, Performance and Accounting in Solaris 2.0" manual states that NFS servers with 32Mb of RAM, up to four disks and up to ten logged in users maxusers should be set to 64. With more disks and users it should be set to 128.

Table 5 Default Settings for Kernel Parameters

| Kernel Table | Variable   | Default Setting                 |

|--------------|------------|---------------------------------|

| Callout      | ncallout   | 16 + max_nprocs                 |

| Inode        | ufs_ninode | max_nprocs + 16 + maxusers + 64 |

| Name Cache   | ncsize     | max_nprocs + 16 + maxusers + 64 |

Table 5 Default Settings for Kernel Parameters

| Kernel Table | Variable   | Default Setting                         |

|--------------|------------|-----------------------------------------|

| Process      | max_nprocs | 10 + 16 * maxusers (must be under 4096) |

| Quota Table  | ndquot     | (maxusers * NMOUNT)/4 + max_nprocs      |

| User Process | maxuprc    | max_nprocs - 5                          |

#### Directory Name Lookup Cache (dnlc)

This is sized using maxusers and a large cache size (ncsize above) significantly helps NFS servers which have lots of clients<sup>1</sup>. The command vmstat -s shows the DNLC hit rate. Directory names less than 14 characters long are cached and names that are too long are reported as well. A cache miss means that a disk I/O may be needed to read the directory when traversing the pathname components to get to a file. A hit rate of much less than 70% may need attention.

```

% vmstat -s

... lines omitted

29600 total name lookups (cache hits 82% per-process)

toolong 3077

```

#### Pstat in SunOS 4.X

The occupancy and size of some of these tables can be seen using the pstat -T command. This is for a SPARCstation 1 running SunOS 4.1.1 with maxusers set to 8.

```

% pstat -T

217/582 filesThe system wide open file table

166/320 inodesThe inode cache

48/138 processesThe system wide process table

13948/31756 swapKilobytes of swap used out of the total

```

The pstat command only shows a few of the tables. Before SunOS 4.1 it showed another entry, confusingly also labelled files, which was in fact the number of streams. From SunOS 4.1 on the number of streams is increased dynamically on demand so this entry was removed.

<sup>1.</sup> See "Networks and File Servers: A Performance Tuning Guide

#### Inode Cache

The inode cache is used whenever an operation is performed on an entity in the UFS filesystem. The inode read from disk is cached in case it is needed again. An IO benchmark which opened and closed a large number of files could be tuned by increasing the size of the inode cache such that it produced results showing a slow SCSI disk performing at an apparent rate of over 10 Mbytes per second. Since the benchmark was claimed to be representative of common disk usage patterns a large inode cache can help I/O intensive programs significantly. Other versions of Unix (apart from SVR4), which use a different virtual memory and I/O setup, produced results for this benchmark that were an order of magnitude slower. The inode cache seems to grow dynamically at a fairly slow rate if it is used intensively and increasing maxusers provides a much larger initial size for the cache.

#### Buffer Cache

The buffer cache is used to cache all UFS disk I/O in SunOS 3 and BSD Unix. In SunOS 4 and SVR4 it is used to cache inode and cylinder group related disk I/O only. It is set via the kernel variable nbuf and is usually set to around 32. It should be increased to 64 for machines with up to four disks and 112 for machines with more than four disks<sup>1</sup>. For SunOS 4.1.2 and 4.1.3 it is no longer necessary to set nbuf as it is sized automatically.

### Solaris 2.0 Tuning

There is a manual section called "Administering Security, Performance and Accounting in Solaris 2.0". Read it!

There is a bug in the C library implementation of localtime which means that some timezone settings cause the zoneinfo file to be reread on every call to localtime or mktime. This occurs when the symbolic timezone names are used, e.g. GB-Eire or US/Pacific. The work-around is to use a descriptive timezone name such as GMT0BST (rather than GB-Eire) or PST8PDT (rather than US/Pacific) where the zone can be determined directly rather than using the zoneinfo data. The dates that summer time start/stop may be inaccurate

<sup>1.</sup> Details are in "Tuning the SPARCserver 490 for Optimal NFS Performance, February 1991

but some applications like Calendar Manager run many times faster and a simple 1s -1 is noticeably quicker. This is fixed in Solaris 2.1 by reading the zoneinfo file once and caching it for future use.

#### Solaris 2.1 Performance

Solaris 2.1 has had a large amount of performance tuning work done on it. It is substantially faster than Solaris 2.0 and performs at a similar level to SunOS 4.1.3 on uniprocessor machines. On multiprocessor machines Solaris 2.1 is often faster than SunOS 4.1.3. See the chapter on multiprocessors.

### Paging, MMU Algorithms And PMEGS

#### Sar in Solaris 2

This utility has a huge number of options and some very powerful capabilities. One of its best features is that you can log its full output in date-stamped binary form to a file. You can even look at a few selected measures then go back to look at all the other measures if you need to. It is described in full in "Administering Security, Performance and Accounting in Solaris 2.0" and in "System Performance Tuning, Mike Loukides, O'Reilly".

#### Vmstat

The paging activity on a Sun can be monitored using vmstat. SunOS 4.1.1 output is shown below. Solaris 2.0 reuses the avm field to show free swap space.

| 8     | vms | stat   | 5   |      |    |    |     |    |    |    |      |    |    |    |        |     |     |     |    |    |    |

|-------|-----|--------|-----|------|----|----|-----|----|----|----|------|----|----|----|--------|-----|-----|-----|----|----|----|

| procs |     | memory |     | page |    |    |     |    |    |    | disk |    |    |    | faults |     |     | cpu |    |    |    |

| r     | b   | W      | avm | fre  | re | at | рi  | ро | fr | de | sr   | s0 | s1 | d2 | s3     | in  | sy  | CS  | us | sy | id |

| 0     | 0   | 0      | 0   | 1072 | 0  | 2  | 4   | 1  | 3  | 0  | 1    | 1  | 0  | 0  | 0      | 43  | 217 | 15  | 7  | 4  | 89 |

| 1     | 0   | 0      | 0   | 996  | 0  | 4  | 0   | 0  | 0  | 0  | 0    | 4  | 0  | 0  | 0      | 112 | 573 | 25  | 11 | 6  | 83 |

| 0     | 0   | 0      | 0   | 920  | 0  | 0  | 0   | 0  | 0  | 0  | 0    | 0  | 0  | 0  | 0      | 178 | 586 | 43  | 25 | 9  | 67 |

| 0     | 0   | 0      | 0   | 900  | 0  | 0  | 0   | 0  | 0  | 0  | 0    | 3  | 0  | 0  | 0      | 127 | 741 | 30  | 13 | 6  | 81 |

| 0     | 0   | 0      | 0   | 832  | 0  | 0  | 4   | 0  | 0  | 0  | 0    | 0  | 0  | 0  | 0      | 171 | 362 | 44  | 7  | 6  | 87 |

| 0     | 0   | 0      | 0   | 780  | 0  | 0  | 72  | 0  | 0  | 0  | 0    | 13 | 0  | 5  | 0      | 158 | 166 | 45  | 3  | 8  | 89 |

| 0     | 3   | 0      | 0   | 452  | 0  | 0  | 100 | 0  | 76 | 0  | 47   | 20 | 0  | 3  | 0      | 200 | 128 | 79  | 6  | 11 | 83 |

| 0     | 0   | 0      | 0   | 308  | 0  | 2  | 28  | 0  | 20 | 0  | 15   | 2  | 0  | 1  | 0      | 69  | 50  | 28  | 3  | 4  | 93 |

| 0     | 0   | 0      | 0   | 260  | 0  | 3  | 8   | 0  | 24 | 0  | 12   | 0  | 0  | 1  | 0      | 44  | 102 | 25  | 5  | 4  | 91 |

| 0     | 0   | 0      | 0   | 260  | 0  | 0  | 0   | 0  | 0  | 16 | 3    | 3  | 0  | 1  | 0      | 42  | 68  | 12  | 3  | 5  | 92 |

|       |     |        |     |      |    |    |     |    |    |    |      |    |    |    |        |     |     |     |    |    |    |

Unfortunately the vmstat manual page, even in SunOS 4.1.1 is misleading in some respects so clarification of some fields is in order. See the manual page.

Table 6 Vmstat fields explained

| Field          | Explanation                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Memory         | Report on usage of real memory.                                                                                                                                             |  |  |  |  |  |  |  |  |

| avm or<br>swap | Active virtual memory is a historical measure that is always set to zero. swap shows the free virtual memory in Kbytes for Solaris 2.0                                      |  |  |  |  |  |  |  |  |

| fre            | Free real memory in Kbytes                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Page           | Report information about page faults and paging activity. The information on each of the following activities is averaged each five seconds, and given in units per second. |  |  |  |  |  |  |  |  |

| re             | pages reclaimed from the free list                                                                                                                                          |  |  |  |  |  |  |  |  |

| at             | number of attaches to pages already in use by other processes                                                                                                               |  |  |  |  |  |  |  |  |

| pi             | kilobytes per second paged in                                                                                                                                               |  |  |  |  |  |  |  |  |

| po             | kilobytes per second paged out                                                                                                                                              |  |  |  |  |  |  |  |  |

| fr             | kilobytes freed per second                                                                                                                                                  |  |  |  |  |  |  |  |  |

| de             | artificial memory deficit set during swap out to prevent immediate swapin                                                                                                   |  |  |  |  |  |  |  |  |

| sr             | pages scanned by clock algorithm, per-second                                                                                                                                |  |  |  |  |  |  |  |  |

Looking at the above log of vmstat it can be seen that some CPU activity in the first few entries was entirely memory resident. This was followed by some paging and as the free memory dropped below 256K the scanning algorithm woke up and started to look for pages that could be reused to keep the free list above its 256K minimum. The five second average shows that the result of this is a free list at around 300K. This is typical for a Sun that has been running for a while and is not idle. If the free list is consistently greater than 1 Mb on pre 4.1.1 SunOS releases you may have a PMEG problem!

### The Sun-4 MMU - sun4, sun4c, sun4e kernel architectures

Older Sun machines use a "Sun-4" hardware memory management unit which acts as a large cache for memory translations. It is much larger than the MMU translation cache found on more recent systems but the entries in the cache, known as PMEGs are larger and take longer to load. A PMEG is a Page Map Entry Group, a contiguous chunk of virtual memory made up of 32 or 64

physical 8Kb or 4Kb page translations. A SPARCstation 1 has a cache containing 128 PMEGS so a total of 32Mb of virtual memory can be cached. The number of PMEGS on each type of Sun is shown in Table 5-2.

Table 7 Sun-4 MMU Characteristics

| Processor type   | Page Size | Pages/PMEG | PMEGS | Total VM | Contexts |

|------------------|-----------|------------|-------|----------|----------|

| SS1(+), SLC, IPC | 4 Kb      | 64         | 128   | 32 Mb    | 8        |

| ELC              | 4 Kb      | 64         | 128   | 32 Mb    | 8        |

| SPARCengine 1E   | 8 Kb      | 32         | 256   | 64 Mb    | 8        |

| IPX              | 4 Kb      | 64         | 256   | 64 Mb    | 8        |

| SS2              | 4 Kb      | 64         | 256   | 64 Mb    | 16       |

| Sun 4/110, 150   | 8 Kb      | 32         | 256   | 64 Mb    | 16       |

| Sun 4/260, 280   | 8 Kb      | 32         | 512   | 128 Mb   | 16       |

| SPARCsystem 300  | 8 Kb      | 32         | 256   | 64 Mb    | 16       |

| SPARCsystem 400  | 8 Kb      | 32         | 1024  | 256 Mb   | 64       |

In SunOS 4.0.3 and SunOS 4.1 there were two independent problems which only came to light when Sun started to ship 4Mbit DRAM parts and the maximum memory on a SPARCstation 1 went up from 16 Mb to 40Mb. Memory prices also dropped and many more people loaded up their SPARCstation 1,1+, SLC or IPC with extra RAM. When the problem was discovered a patch was made for SunOS 4.0.3 and SunOS 4.1. The patch is incorporated into DBE 1.0 and later and SunOS 4.1.1 and later as standard.

If you run within the limits of the MMU's 128 PMEG entries the processor runs flat out; faster than other MMU architectures in fact. When you run outside the limits of the MMU the problems occur.

#### PMEG reload time problem

When a new PMEG was needed the kernel had to get information from a number of data structures and process it to produce the values needed for the PMEG entry. This took too long and one of the symptoms of PMEG thrashing was that the system CPU time is very high, often over 50% for no apparent reason. The cure is to provide a secondary, software cache for the completed PMEG entries which can be resized if required. If a PMEG entry is already in

the software cache then it is block copied into place. The effect is that the reload time is greatly reduced and the amount of system CPU used drops back to more reasonable levels.

#### PMEG Stealing

In order to load a new PMEG the kernel had to decide which existing entry to overwrite. The original algorithm used made the problem much worse since it often stole a PMEG from an active process, which would then steal it back again, causing a thrashing effect. When a PMEG was stolen its pages were put onto the free list. If every PMEG was stolen from a process then every page would be on the free list and the system would decide to swap out the process. This gave rise to another symptom of PMEG thrashing, a large amount of free memory reported by vmstat and a lot of swapping reported by vmstat —S even though there was no disk I/O going on. The cure is to use a much better algorithm for deciding which PMEG to reuse and to stop putting pages on the free list when a PMEG is stolen.

#### Problem Solved

There are some performance graphs in the "SPARCstation 2 Performance Brief" which show the difference between SunOS 4.1 and SunOS 4.1.1 using a worst case test program. For a SPARCstation IPC the knee in the curve which indicates the onset of PMEG thrashing is at 16 Mb for SunOS 4.1 and around 60 Mb for SunOS 4.1.1. Beyond that point SunOS 4.1 hits a brick wall at 24 Mb while the IPC is degrading gracefully beyond 80 Mb with SunOS 4.1.1.

The SPARCstation 2, which has twice as many PMEGs, is flat beyond 80 Mb with no degradation.

If you are called upon to tune a system that seems to have the symptoms described above, is running SunOS 4.0.3 or SunOS 4.1 and you cannot upgrade to SunOS 4.1.1, then you should contact the Sun Answer Centre to get hold of the PMEGS patch.

#### Context s

Table 7 on page 37 shows the number of hardware contexts built into each machine. A hardware context can be though of as a tag on each PMEG entry in the MMU which indicates which process that translation is valid for. This allows the MMU to keep track of the mappings for 8, 16 or 64 processes in the

MMU, depending upon the machine. When a context switch occurs, if the new process is assigned to one of the hardware contexts, then some of its mappings may still be in the MMU and a very fast context switch can take place. For up to the number of hardware contexts available this scheme is more efficient than a more conventional TLB based MMU. When the number of processes trying to run exceeds the number of hardware contexts the kernel has to choose one of the hardware contexts to be reused and has to invalidate all the PMEGS for that context and load some PMEGS for the new context. The context switch time starts to degrade gradually and probably becomes worse than a TLB based system when there are more than twice as many active processes as contexts. This is one reason why a SPARCserver 490 can handle many more users in a timesharing environment than the (apparently faster) SPARCstation 2, which would spend more time in the kernel shuffling the PMEGS in and out of its MMU. There is also a difference in the hardware interface used to control the MMU and cache, with more work needing to be done in software to flush a context on a SPARCstation 1 and higher level hardware support on a SPARCstation 2 or SPARCserver 400.

No new machines are being designed to use this type of MMU, but it represents the bulk of the installed base.

# The SPARC Reference MMU - sun4m kernel architecture

Recently Sun's have started to use the SPARC Reference MMU which has an architecture that is similar to many other MMU's in the rest of the industry.

Table 8 SPARC Reference MMU Characteristics

| Processor Types                       | Page Sizes | TLB Entries | Contexts | Total VM |

|---------------------------------------|------------|-------------|----------|----------|

| Ross 6002 Modules                     | 4 Kb       | 64          | 4096     | 256Kb    |

| Cypress 604 and 605 MMU's             | 256Kb      |             |          | 16Mb     |

| SPARCserver 600 -120 and -140         | 16Mb       |             |          | 1024Mb   |

| Tadpole SPARCbook 1                   |            |             |          |          |

| Texas Instruments SuperSPARC          | 4 Kb       | 64          | 65536    | 256Kb    |

| SPARCserver 600 -41, -52 and -54      | 256Kb      |             |          | 16Mb     |

| SPARCstation 10 -30, -41, -52,and -54 | 16Mb       |             |          | 1024Mb   |

| Fujitsu SPARClite embedded CPU        | 4 Kb       | 32          | 256      | 128Kb    |

| •                                     | 256Kb      |             |          | 8Mb      |

|                                       | 16Mb       |             |          | 512Mb    |

| Texas Instruments MicroSPARC          | 4Kb        | 32          | 64       | 128Kb    |

| SPARCclassic and SPARCstation LX      | 256Kb      |             |          | 8Mb      |

|                                       | 16Mb       |             |          | 512Mb    |

There are four current implementations, the Cypress uniprocessor 604 and multiprocessor 605 MMU chips, the MMU that is integrated into the SuperSPARC chip, the Fujitsu SPARClite and the highly integrated MicroSPARC (which I do not have full details of yet).

In this case there is a small fully associative cache for address translations (a Translation Lookaside Buffer or TLB) which typically has 64 entries that map one contiguous area of virtual memory each. These areas are usually a single 4Kb page but future releases of Solaris 2 may be optimised to use the 256Kb or 16Mb modes in certain cases. Each of the 64 entries has a tag that indicates what context it belongs to. This means that the MMU does not have to be flushed on a context switch. The tag is 12 bits on the Cypress/Ross MMU and 16 bits on the SuperSPARC MMU, giving rise to a much larger number of hardware contexts than the Sun-4 MMU so that MMU performance is not a problem when very large numbers of users or processes are present.

The primary difference from the Sun-4 MMU is that TLB entries are loaded automatically by table walking hardware in the MMU. The CPU stalls for a few cycles waiting for the MMU but unlike many other TLB based MMU's or the Sun-4 MMU the CPU does not take a trap to reload the entries itself. The kernel builds a table in memory that contains all the valid virtual memory mappings and loads the address of the table into the MMU once at boot time. The size of this table is large enough for most purposes but a system with a large amount of active virtual memory can cause a shortage of page table entries with similar effects to a PMEGS shortage. The solution is simply to increase the amount of kernel memory allocated to this purpose. The kernel variable npts controls how many are allocated. It is calculated depending upon the amount of physical memory in the system but can be set explicitly by patching npts. On a 64Mb SPARCserver 600 running a GENERIC 4.1.2 kernel npts is set to 1065 which seems on the low side to me. Both DBE 1.2 and SunOS 4.1.3 set npts much higher.

The Sun4-MMU based systems can cache sufficient virtual memory translations to run programs many Mb in size with no MMU reloads. When the MMU limits are exceeded there is a large overhead. The SPARC Reference MMU only caches 64 pages of 4Kb at a time in normal use for a total of 256Kb. The MMU is reloading continuously but it has an exceptionally fast reload.

# The Paging Algorithm

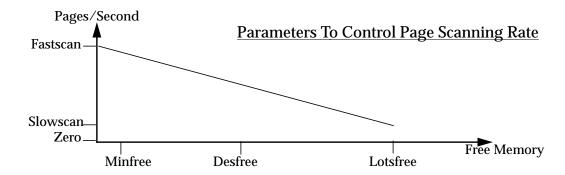

When new pages are allocated from the free list there comes a point when the system decides that there is no longer enough free memory (less than lotsfree) and it goes to look for some pages that haven't been used recently to add to the free list. At this point the pagedaemon is woken up. The system also checks the size of the free list four times per second and may wake up the pagedaemon. After a wakeup the pagedaemon is scheduled to run as a process inside the kernel and assumes that it runs four times per second so it calculates a scan rate then divides by four to get the number of pages to scan before it goes back to sleep.

The pagedaemon's scanning algorithm works by regarding all the pagable RAM in order of its physical address as if it was arranged in a circle. Two pointers are used like the hands of a clock and the distance between the two hands is controlled by handspread. When there is a shortage of free pages (less than lotsfree) the hands start to move round the clock at a slow rate (slowscan) which increases linearly to a faster rate (fastscan) as free memory tends to zero. If the pages for each hand are not locked into memory,

on the free list or otherwise busy then a flag which is set every time the pages are referenced is examined and if they have not been referenced the pages can be freed. The first hand then clears the referenced flag for its page so that when the second hand gets round to the page it will be freed unless it has been referenced since the first hand got there. If the freed page contained modified data it is paged out to disk. If there is a lot of memory in the system then the chances of an individual page being referenced by a CPU in a given time span are reduced so the spread of the hands must be increased to compensate.

If the shortage of memory gets worse (less than desfree), there are two or more processes in the run queue, and it stays at that level for more than 30 seconds then swapping will begin. If it gets to a minimum level (minfree) swapping starts immediately. If after going twice through the whole of memory there is still a shortage, the swapper is invoked to swap out entire processes. The algorithm limits the number of pages scheduled to be paged out to 40 per second (maxpgio) since this is a good figure for the number of random I/Os per second on a single disk. If you have swap spread across several disks then increasing maxpgio may improve paging performance and delay the onset of swapping. Note that vmstat po reports the number of kilobytes per second paged out which can be compared to maxpgio \* pagesize.

# Kernel Variables To Control Paging

#### minfree

This is the absolute minimum memory level that can be tolerated by the system. If (freemem - deficit) is less than minfree the system will immediately swap processes out rather than paging. It is often set to 8 pages and clamped at desfree/2. The SunOS 4 sun4m kernel has a higher default and Solaris 2.1 scales the value.

#### desfree

This represents a *desperation* level, if free memory stays below this level for more than 30 seconds then paging is abandoned and swapping begins. It is often set to 25 pages and is clamped to (total memory)/16. The SunOS 4 sun4m kernel has a higher default and Solaris 2.1 scales the value.

#### lotsfree

This is the memory limit that triggers the page daemon to start working if free memory drops below it. It is often set to 64 pages and is clamped at (total memory)/8. The sun4m kernel has a higher default of around 500 pages and Solaris 2.1 scales the value.

#### fastscan

This is the number of pages scanned per second by the algorithm when there is minfree available and it is often set to 1000. There is a linear ramp up from slowscan to fastscan as free memory goes from lotsfree to zero. The SunOS 4.X sun4m kernel sets it to (total memory in pages)/2. The Solaris 2.1 kernel also scales up by the amount of RAM in the system.

#### slowscan

This is the number of pages scanned per second by the algorithm when there is just under lotsfree available and it is often set to 100. There is a linear ramp up from slowscan to fastscan as free memory goes from lotsfree to zero. The sun4m kernel has a higher default of fastscan/10.

#### maxpgio

This is the maximum number of page out I/O operations per second that the system will schedule. The default is 40 pages per second, which is set to avoid saturating random access to a single 3600 rpm (60 rps) disk at two-thirds of the rotation rate. It can be increased if more or faster disks are being used for the swap space. Many systems now have 5400 rpm (90 rps) disks, see Table 14 on page 69 for disk specifications.

### handspread

Handspread is set to (total memory)/4, but is increased to be at least as big as fastscan which makes it (total memory)/2 on sun4m machines.

Unfortunately, in the old days of Berkeley Unix, when an 8 Mb VAX 750 was a big machine, the code that set up handspread clamped it to a maximum of 2 Mb. This code was fixed in SunOS 4.1.1 so handspread needs to be patched on any machine that has much more than 8 Mb of RAM and is running SunOS 4.1 or before.

The default value in /vmunix is 0 which makes the code calculate its own value. In this case, just under 4 Mb since this machine has 16Mb of RAM and is running SunOS 4.1.1.

# adb -k -w /vmunix /dev/mem

physmem ff3

handspread?X

\_handspread:

\_handspread:

0

handspread/X

handspread:

\_handspread: 3e8000

If the default value is patched using adb then that value is used rather than worked out from the available RAM. This is how it can be fixed in releases of SunOS prior to 4.1.1, using handspread?W0x3e8000 to patch the value into /vmunix and handspread/W0x3e8000 to patch the value in memory.

The effect of the problem is that pages that are actively being used are more likely to be put on the free list if handspread is too small, causing extra work for the kernel. If the system has a lot of memory installed an stop/go effect can occur where the scanning algorithm will be triggered by a shortage of memory and it will free every page it finds until there is masses of free memory then it

will go to sleep again. On a properly configured system it should be trickling around continuously at a slow rate tidying up the pages that haven't been referenced for a while.

# Swapping Out And How To Get Back In

The kernel keeps track of the ten biggest processes according to their resident set (RSS). For swapping it selects the four largest and swaps out the oldest or a process that has been sleeping longer than maxslp. The deficit (vmstat de) is increased to prevent the process from swapping back in immediately.

The first processes to be swapped back in are the smallest ones that have been asleep for longest and are not running at low priority. A process will be swapped back in when half of the number of pages it freed on swapout are available, although only the basic few pages are swapped in in one go and the rest are paged in as needed.

# Sensible Tweaking